# Hitachi Single-Chip Microcomputer

H8S/2138 Series H8S/2134 Series

Hardware Manual Supplementary Edition

# **HITACHI**

ADE-602-144 Rev. 1.0 8/1/98 © Hitachi, Ltd. 1998

## **Cautions**

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party's

rights, including intellectual property rights, in connection with use of the information

contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# Contents

| Secti | ion 24  | Electrical Characteristics           | 599 |

|-------|---------|--------------------------------------|-----|

| 24.1  | Absolu  | te Maximum Ratings                   | 599 |

| 24.2  | DC Ch   | aracteristics                        | 600 |

| 24.3  | AC Ch   | aracteristics                        | 611 |

|       | 24.3.1  | Clock Timing                         | 612 |

|       | 24.3.2  | Control Signal Timing                | 614 |

|       | 24.3.3  | Bus Timing                           | 616 |

|       | 24.3.4  | Timing of On-Chip Supporting Modules | 623 |

|       |         | onversion Characteristics            |     |

|       |         | onversion Characteristics            |     |

| 24.6  | Flash N | Memory Characteristics               | 636 |

| 24.7  | Usage   | Note                                 | 638 |

|       |         |                                      |     |

| Appe  | endix F | F Product Code Lineup                | 808 |

# Section 24 Electrical Characteristics

# 24.1 Absolute Maximum Ratings

Table 24.1 lists the absolute maximum ratings.

**Table 24.1 Absolute Maximum Ratings**

- Preliminary -

| Item                                              | Symbol           | Value                                                       | Unit |

|---------------------------------------------------|------------------|-------------------------------------------------------------|------|

| Power supply voltage                              | V <sub>cc</sub>  | -0.3 to +7.0                                                | V    |

| Input voltage (except ports 6 and 7)              | $V_{in}$         | $-0.3$ to $V_{cc}$ +0.3                                     | V    |

| Input voltage (CIN input not selected for port 6) | $V_{in}$         | -0.3 to V <sub>cc</sub> +0.3                                | V    |

| Input voltage (CIN input selected for port 6)     | $V_{in}$         | Lower voltage of $-0.3$ to $V_{cc}$ +0.3 and $AV_{cc}$ +0.3 | V    |

| Input voltage (port 7)                            | $V_{in}$         | -0.3 to AV <sub>cc</sub> + 0.3                              | V    |

| Analog power supply voltage                       | $AV_CC$          | -0.3 to +7.0                                                | V    |

| Analog input voltage                              | V <sub>AN</sub>  | -0.3 to AV <sub>cc</sub> +0.3                               | V    |

| Operating temperature                             | T <sub>opr</sub> | Regular specifications: -20 to +75*                         | °C   |

|                                                   |                  | Wide-range specifications: -40 to +85*                      | °C   |

| Storage temperature                               | T <sub>stg</sub> | -55 to +125                                                 | °C   |

Caution: Permanent damage to the chip may result if absolute maximum ratings are exceeded.

<sup>\*</sup> A range of 0 to +75°C must be observed for flash memory programming/erasing in the F-ZTAT version.

## 24.2 DC Characteristics

Table 24.2 lists the DC characteristics. Table 24.3 lists the permissible output currents.

**Table 24.2 DC Characteristics**

- Preliminary -

Conditions:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{CC}^{*1} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = AV_{SS}^{*1} = 0 \text{ V}$ ,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

| Item                     |                                                          |     | Symbol                      | Min                     | Тур | Max                        | Unit | <b>Test Conditions</b>    |

|--------------------------|----------------------------------------------------------|-----|-----------------------------|-------------------------|-----|----------------------------|------|---------------------------|

| Schmitt<br>trigger input |                                                          | (1) | V <sub>T</sub>              | 1.0                     | _   | _                          | V    |                           |

| voltage                  | IRQ5 to IRQ3                                             |     | V <sub>T</sub> <sup>+</sup> | _                       | _   | $V_{\text{CC}} \times 0.7$ | V    | _                         |

|                          |                                                          |     | $V_T^+ - V_T^-$             | 0.4                     | _   | _                          | V    |                           |

| Input high voltage       | RES, STBY,<br>NMI, MD1, MD0                              | (2) | V <sub>IH</sub>             | V <sub>cc</sub> - 0.7   | _   | V <sub>cc</sub> +0.3       | V    |                           |

|                          | EXTAL                                                    | -   |                             | $V_{\rm CC} \times 0.7$ | _   | V <sub>cc</sub> +0.3       | V    | _                         |

|                          | Port 7                                                   | =   |                             | 2.0                     | _   | AV <sub>cc</sub> +0.3      | s V  | _                         |

|                          | Input pins<br>except (1) and<br>(2) above* <sup>6</sup>  |     | _                           | 2.0                     | _   | V <sub>CC</sub> +0.3       | V    | _                         |

| Input low voltage        | RES, STBY,<br>MD1, MD0                                   | (3) | $V_{\text{IL}}$             | -0.3                    | _   | 0.5                        | V    |                           |

|                          | NMI, EXTAL,<br>input pins except<br>(1) and (3)<br>above |     | _                           | -0.3                    | _   | 0.8                        | V    | _                         |

| Output high voltage      | All output pins (except P97, and P52)*5                  |     | V <sub>OH</sub>             | V <sub>cc</sub> -0.5    | _   | _                          | V    | I <sub>OH</sub> = -200 μA |

|                          |                                                          |     |                             | 3.5                     | _   | _                          | V    | I <sub>OH</sub> = -1 mA   |

|                          | P97, P52*4                                               |     | _                           | 2.5                     | _   | _                          | V    | $I_{OH} = -1 \text{ mA}$  |

| Output low               | All output pins*5                                        |     | V <sub>OL</sub>             | _                       | _   | 0.4                        | V    | I <sub>OL</sub> = 1.6 mA  |

| voltage                  | Ports 1 to 3                                             |     |                             | _                       | _   | 1.0                        | V    | I <sub>OL</sub> = 10 mA   |

Conditions:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{CC}^{*1} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = AV_{SS}^{*1} = 0 \text{ V}$ ,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

| Item                                    |                                  |     | Symbol           | Min | Тур  | Max  | Unit | Test Conditions                                        |

|-----------------------------------------|----------------------------------|-----|------------------|-----|------|------|------|--------------------------------------------------------|

| Input<br>leakage                        | RES                              |     | I <sub>in</sub>  | _   | _    | 10.0 | μΑ   | $V_{in} = 0.5 \text{ to} $<br>$V_{CC} - 0.5 \text{ V}$ |

| current                                 | STBY, NMI, MD1,<br>MD0<br>Port 7 |     |                  | _   | _    | 1.0  | μΑ   | _                                                      |

|                                         |                                  |     | _                | _   | _    | 1.0  | μΑ   | $V_{in} = 0.5 \text{ to}$<br>$AV_{CC} - 0.5 \text{ V}$ |

| Three-state leakage current (off state) | Ports 1 to 6<br>Ports 8, 9       |     | I <sub>TSI</sub> | _   | _    | 1.0  | μА   | $V_{in} = 0.5 \text{ to}$ $V_{CC} - 0.5 \text{ V}$     |

| Input pull-                             | Ports 1 to 3                     |     | -I <sub>P</sub>  | 50  | _    | 300  | μΑ   | V <sub>in</sub> = 0 V                                  |

| up MOS<br>current                       | Port 6                           |     |                  | 60  | _    | 500  | μΑ   |                                                        |

| Input capacitance                       | RES                              | (4) | C <sub>in</sub>  | _   | _    | 80   | pF   | V <sub>in</sub> = 0 V<br>f = 1 MHz                     |

|                                         | NMI                              | -   |                  | _   | _    | 50   | pF   | $T_a = 25^{\circ}C$                                    |

|                                         | P52, P97,<br>P42, P86            | •   |                  | _   | _    | 20   | pF   | _                                                      |

|                                         | Input pins except (4) above      |     |                  | _   | _    | 15   | pF   | _                                                      |

| Current dissipation*7                   | Normal operation                 |     | I <sub>cc</sub>  | _   | 75   | 100  | mA   | f = 20 MHz,<br>H8S/2134 Series                         |

|                                         |                                  |     |                  |     | 85   | 120  | mA   | f = 20 MHz,<br>H8S/2138 Series                         |

|                                         | Sleep mode                       |     | _                | _   | 60   | 85   | mA   | f = 20 MHz,<br>H8S/2134 Series                         |

|                                         |                                  |     |                  |     | 70   | 100  | mA   | f = 20 MHz,<br>H8S/2138 Series                         |

|                                         | Standby mode*8                   |     | _                | _   | 0.01 | 5.0  | μΑ   | T <sub>a</sub> ≤ 50°C                                  |

|                                         |                                  |     |                  | _   | _    | 20.0 | μΑ   | 50°C < T <sub>a</sub>                                  |

| Analog<br>power                         | During A/D, D/A conversion       |     | Al <sub>cc</sub> | _   | 3.2  | 7.0  | mA   |                                                        |

| supply<br>current                       | Idle                             |     |                  | _   | 0.01 | 5.0  | μΑ   | AV <sub>cc</sub> =<br>2.0 V to 5.5 V                   |

Conditions:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{CC}^{*1} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = AV_{SS}^{*1} = 0 \text{ V}$ ,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

| Item                          | Symbol    | Min | Тур | Max | Unit | <b>Test Conditions</b> |

|-------------------------------|-----------|-----|-----|-----|------|------------------------|

| Analog power supply voltage*1 | $AV_CC$   | 4.5 | _   | 5.5 | V    | Operating              |

|                               |           | 2.0 | _   | 5.5 | V    | Idle/not used          |

| RAM standby voltage           | $V_{RAM}$ | 2.0 | _   | _   | V    |                        |

Notes: 1. Do not leave the AVCC, and AVSS pins open even if the A/D converter and D/A converter are not used.

Even if the A/D converter and D/A converter are not used, apply a value in the range 2.0 V to 5.5 V to AVCC by connection to the power supply ( $V_{cc}$ ), or some other method.

- 2. P67 to P60 include supporting module inputs multiplexed on those pins.

- 3. IRQ2 includes the ADTRG signal multiplexed on that pin.

- P52/SCK0/SCL0 and P97/SDA0 are NMOS push-pull outputs.

An external pull-up resistor is necessary to provide high-level output from SCL0 and SDA0 (ICE = 1).

- P52/SCK0 and P97 (ICE = 0) high levels are driven by NMOS.

- 5. When ICE = 0. Low-level output when the bus drive function is selected is determined separately.

- 6. The upper limit of the port 6 applied voltage is  $V_{cc}$  + 0.3 V when CIN input is not selected, and the lower of  $V_{cc}$  + 0.3 V and  $AV_{cc}$  + 0.3 V when CIN input is selected. When a pin is in output mode, the output voltage is equivalent to the applied voltage.

- 7. Current dissipation values are for  $V_{IH}$  min =  $V_{CC} 0.5$  V and  $V_{IL}$  max = 0.5 V with all output pins unloaded and the on-chip pull-up MOSs in the off state.

- 8. The values are for  $V_{RAM} \le V_{CC} < 4.5 \text{V}$ ,  $V_{IH} \text{ min} = V_{CC} \times 0.9$ , and  $V_{IL} \text{ max} = 0.3 \text{ V}$ .

Conditions:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{ V*}^7, \text{AV}_{CC}^{*1} = 4.0 \text{ V to } 5.5 \text{ V}, \text{V}_{SS} = \text{AV}_{SS}^{*1} = 0 \text{ V}, \text{T}_a = -20 \text{ to } +75^{\circ}\text{C*}^7 \text{ (regular specifications)}, \text{T}_a = -40 \text{ to } +85^{\circ}\text{C*}^7 \text{ (wide-range specifications)}$

| Item                |                                                         |     | Symbol                      | Min                     | Тур | Max                        | Unit | Test Conditions                                       |

|---------------------|---------------------------------------------------------|-----|-----------------------------|-------------------------|-----|----------------------------|------|-------------------------------------------------------|

|                     | IRQ2 to IRQ0*3,                                         | (1) | $V_T^-$                     | 1.0                     | _   | _                          | V    | V <sub>cc</sub> =<br>4.5 V to 5.5 V                   |

| voltage             | IRQ5 to IRQ3                                            |     | V <sub>T</sub> <sup>+</sup> | _                       | _   | $V_{\text{CC}} \times 0.7$ | V    |                                                       |

|                     |                                                         |     | $V_T^+ - V_T^-$             | 0.4                     | _   | _                          | V    | _                                                     |

|                     |                                                         |     | V <sub>T</sub>              | 0.8                     | _   | _                          | V    | V <sub>cc</sub> < 4.5 V                               |

|                     |                                                         |     | V <sub>T</sub> <sup>+</sup> | _                       | _   | $V_{cc} \times 0.7$        | V    | _                                                     |

|                     |                                                         |     | $V_T^+ - V_T^-$             | 0.3                     | _   | _                          | V    | _                                                     |

| Input high voltage  | RES, STBY,<br>NMI, MD1, MD0                             | (2) | V <sub>IH</sub>             | V <sub>cc</sub> - 0.7   | _   | V <sub>cc</sub> +0.3       | V    |                                                       |

|                     | EXTAL                                                   |     |                             | $V_{\rm CC} \times 0.7$ | _   | V <sub>cc</sub> +0.3       | V    | _                                                     |

|                     | Port 7                                                  |     |                             | 2.0                     | _   | AV <sub>cc</sub> +0.3      | 3 V  | _                                                     |

|                     | Input pins<br>except (1) and<br>(2) above* <sup>6</sup> |     | _                           | 2.0                     | _   | V <sub>CC</sub> +0.3       | V    | _                                                     |

| Input low voltage   | RES, STBY,<br>MD1, MD0                                  | (3) | $V_{IL}$                    | -0.3                    | _   | 0.5                        | V    |                                                       |

|                     | NMI, EXTAL,<br>input pins except<br>(1) and (3) above   |     | _                           | -0.3                    |     | 0.8                        | V    |                                                       |

| Output high voltage | All output pins (except P97, and                        |     | V <sub>OH</sub>             | V <sub>cc</sub> -0.5    | _   | _                          | V    | I <sub>OH</sub> = -200 μA                             |

|                     | P52)* <sup>5</sup>                                      |     |                             | 3.5                     | _   | _                          | V    | $I_{OH} = -1 \text{ mA},$ $V_{CC} =$ 4.5 V to 5.5 V   |

|                     |                                                         |     |                             | 3.0                     | _   | _                          | V    | $I_{OH} = -1 \text{ mA},$<br>$V_{CC} < 4.5 \text{ V}$ |

|                     | P97, P52*4                                              |     | _                           | 2.0                     | _   | _                          | V    | $I_{OH} = -1 \text{ mA}$                              |

| Output low          | All output pins*5                                       |     | V <sub>OL</sub>             | _                       | _   | 0.4                        | V    | I <sub>OL</sub> = 1.6 mA                              |

| voltage             | Ports 1 to 3                                            |     | _                           | _                       | _   | 1.0                        | V    | I <sub>OL</sub> = 10 mA                               |

Conditions:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{ V*}^7, \text{AV}_{CC}^{*1} = 4.0 \text{ V to } 5.5 \text{ V}, \text{V}_{SS} = \text{AV}_{SS}^{*1} = 0 \text{ V}, \text{T}_a = -20 \text{ to } +75^{\circ}\text{C*}^7 \text{ (regular specifications)}, \text{T}_a = -40 \text{ to } +85^{\circ}\text{C*}^7 \text{ (wide-range specifications)}$

| Item                                    |                             |     | Symbol           | Min | Тур  | Max  | Unit | Test Conditions                                        |

|-----------------------------------------|-----------------------------|-----|------------------|-----|------|------|------|--------------------------------------------------------|

| Input                                   | RES                         |     | I <sub>in</sub>  | _   | _    | 10.0 | μΑ   | V <sub>in</sub> = 0.5 to                               |

| leakage<br>current                      | STBY, NMI, MD1<br>MD0       | ,   | _                | _   | _    | 1.0  | μΑ   | _ V <sub>cc</sub> − 0.5 V                              |

|                                         | Port 7                      |     | _                | _   | _    | 1.0  | μΑ   | $V_{in} = 0.5 \text{ to}$<br>$AV_{CC} - 0.5 \text{ V}$ |

| Three-state leakage current (off state) | Ports 1 to 6<br>Ports 8, 9  |     | I <sub>TSI</sub> | _   | _    | 1.0  | μА   | $V_{in}$ = 0.5 to $V_{CC}$ - 0.5 V                     |

| Input pull-<br>up current               | Ports 1 to 3                |     | -I <sub>P</sub>  | 50  | _    | 300  | μΑ   | $V_{in} = 0 \text{ V},$ $V_{CC} = 4.5 \text{ V to}$    |

|                                         | Port 6                      |     | _                | 60  | _    | 500  | μΑ   | 5.5 V                                                  |

|                                         | Ports 1 to 3 Port 6         |     | _                | 30  | _    | 200  | μΑ   | V <sub>in</sub> = 0 V,<br>V <sub>CC</sub> < 4.5 V      |

|                                         |                             |     |                  | 40  | _    | 400  | μΑ   | _                                                      |

| Input capacitance                       | RES                         | (4) | C <sub>in</sub>  | _   | _    | 80   | pF   | V <sub>in</sub> = 0 V,<br>f = 1 MHz,                   |

|                                         | NMI                         |     |                  | _   | _    | 50   | pF   | $T_a = 25^{\circ}C$                                    |

|                                         | P52, P97,<br>P42, P86       |     |                  | _   | _    | 20   | pF   | _                                                      |

|                                         | Input pins except (4) above |     | _                | _   | _    | 15   | pF   | _                                                      |

| Current dissipation*8                   | Normal operation            |     | I <sub>cc</sub>  | _   | 65   | 85   | mA   | f = 16 MHz,<br>H8S/2134 Series                         |

|                                         |                             |     |                  | _   | 70   | 100  | mA   | f = 16 MHz,<br>H8S/2138 Series                         |

|                                         | Sleep mode                  |     | _                | _   | 50   | 70   | mA   | f = 16 MHz,<br>H8S/2134 Series                         |

|                                         |                             |     |                  | _   | 60   | 85   | mA   | f = 16 MHz,<br>H8S/2138 Series                         |

|                                         | Standby mode*9              |     | _                | _   | 0.01 | 5.0  | μΑ   | $T_a \le 50^{\circ}C$                                  |

|                                         |                             |     |                  | _   | _    | 20.0 | μΑ   | 50°C < T <sub>a</sub>                                  |

Conditions:  $V_{CC} = 4.0 \text{ V}$  to 5.5  $V^{*7}$ ,  $AV_{CC}^{*1} = 4.0 \text{ V}$  to 5.5 V,  $V_{SS} = AV_{SS}^{*1} = 0 \text{ V}$ ,  $T_a = -20 \text{ to} +75^{\circ}\text{C}^{*7}$  (regular specifications),  $T_a = -40 \text{ to} +85^{\circ}\text{C}^{*7}$  (wide-range specifications)

| ltem                          |                            | Symbol           | Min | Тур  | Max | Unit | <b>Test Conditions</b>                      |

|-------------------------------|----------------------------|------------------|-----|------|-----|------|---------------------------------------------|

| Analog<br>power               | During A/D, D/A conversion | Al <sub>cc</sub> | _   | 3.2  | 7.0 | mA   |                                             |

| supply<br>current             | Idle                       |                  | _   | 0.01 | 5.0 | μΑ   | $AV_{CC} = 2.0 \text{ V to } 5.5 \text{ V}$ |

| Analog power supply voltage*1 |                            | AV <sub>cc</sub> | 4.0 | _    | 5.5 | V    | Operating                                   |

|                               |                            |                  | 2.0 | _    | 5.5 | V    | Idle/not used                               |

| RAM standby voltage           |                            | $V_{RAM}$        | 2.0 | _    | _   | V    |                                             |

Notes: 1. Do not leave the AVCC, and AVSS pins open even if the A/D converter and D/A converter are not used.

Even if the A/D converter and D/A converter are not used, apply a value in the range 2.0 V to 5.5 V to AVCC by connection to the power supply ( $V_{cc}$ ), or some other method.

- 2. P67 to P60 include supporting module inputs multiplexed on those pins.

- 3. IRQ2 includes the ADTRG signal multiplexed on that pin.

- P52/SCK0/SCL0 and P97/SDA0 are NMOS push-pull outputs.

An external pull-up resistor is necessary to provide high-level output from SCL0 and SDA0 (ICE = 1).

P52/SCK0 and P97 (ICE = 0) high levels are driven by NMOS.

- When ICE = 0. Low-level output when the bus drive function is selected is determined separately.

- 6. The upper limit of the port 6 applied voltage is  $V_{cc}$  + 0.3 V when CIN input is not selected, and the lower of  $V_{cc}$  + 0.3 V and  $AV_{cc}$  + 0.3 V when CIN input is selected. When a pin is in output mode, the output voltage is equivalent to the applied voltage.

- 7. Ranges of  $V_{\rm CC}$  = 4.5 to 5.5 V and  $T_{\rm a}$  = 0 to +75°C must be observed for flash memory programming/erasing.

- 8. Current dissipation values are for  $V_{IH}$  min =  $V_{CC} 0.5$  V and  $V_{IL}$  max = 0.5 V with all output pins unloaded and the on-chip pull-up MOSs in the off state.

- 9. The values are for  $V_{RAM} \le V_{CC} < 4.5 \text{ V}$ ,  $V_{IH} \text{ min} = V_{CC} \times 0.9$ , and  $V_{IL} \text{ max} = 0.3 \text{ V}$ .

Conditions\*<sup>7</sup>:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, \text{ AV}_{CC}^{*1} = 2.7 \text{ V to } 5.5 \text{ V}, \text{ V}_{SS} = \text{AV}_{SS}^{*1} = 0 \text{ V},$   $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications)

| Item                |                                                         |     | Symbol                      | Min                   | Тур | Max                        | Unit | Test Conditions                                                                                                                                                                             |

|---------------------|---------------------------------------------------------|-----|-----------------------------|-----------------------|-----|----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | $\overline{IRQ2}$ to $\overline{IRQ0}*^3$ ,             | (1) | $V_T^-$                     | $V_{cc} \times 0.2$   | _   | _                          | V    |                                                                                                                                                                                             |

| voltage             | IRQ5 to IRQ3                                            |     | V <sub>T</sub> <sup>+</sup> | _                     | _   | $V_{\text{CC}} \times 0.7$ | V    | _                                                                                                                                                                                           |

|                     |                                                         |     | $V_T^+ - V_T^-$             | $V_{cc} \times 0.05$  | _   | _                          | V    | _                                                                                                                                                                                           |

| Input high voltage  | RES, STBY,<br>NMI, MD1, MD0                             | (2) | V <sub>IH</sub>             | $V_{cc} \times 0.9$   | _   | V <sub>cc</sub> +0.3       | V    |                                                                                                                                                                                             |

|                     | EXTAL                                                   |     |                             | $V_{CC} \times 0.7$   | _   | V <sub>cc</sub> +0.3       | V    | _                                                                                                                                                                                           |

|                     | Port 7                                                  |     |                             | $V_{CC} \times 0.7$   | _   | AV <sub>cc</sub> +0.3      | 3 V  | _                                                                                                                                                                                           |

|                     | Input pins<br>except (1) and<br>(2) above* <sup>6</sup> |     |                             | $V_{CC} \times 0.7$   | _   | V <sub>cc</sub> +0.3       | V    | _                                                                                                                                                                                           |

| Input low voltage   | RES, STBY,<br>FWE, MD1, MD0                             | (3) | V <sub>IL</sub>             | -0.3                  | _   | $V_{cc} \times 0.1$        | V    |                                                                                                                                                                                             |

|                     | NMI, EXTAL, input pins except                           |     | _                           | -0.3                  | _   | $V_{cc} \times 0.2$        | V    | V <sub>CC</sub> < 4.0 V                                                                                                                                                                     |

|                     | (1) and (3)<br>above                                    |     |                             |                       |     | 0.8                        | V    | V <sub>CC</sub> = 4.0 V to 5.5 V                                                                                                                                                            |

| Output high voltage | All output pins (except P97, and                        |     | V <sub>OH</sub>             | V <sub>cc</sub> – 0.5 | _   | _                          | V    | I <sub>OH</sub> = -200 μA                                                                                                                                                                   |

|                     | P52)* <sup>5</sup>                                      |     |                             | V <sub>cc</sub> – 1.0 | _   | _                          | V    | $I_{OH} = -1 \text{ mA}$<br>( $V_{CC} < 4.0 \text{ V}$ )                                                                                                                                    |

|                     | P97, P52*4                                              |     | _                           | 1.0                   | _   | _                          | V    | I <sub>OH</sub> = -1 mA                                                                                                                                                                     |

| Output low          | All output pins*5                                       |     | $V_{OL}$                    | _                     | _   | 0.4                        | V    | $I_{OL} = 0.8 \text{ mA}$                                                                                                                                                                   |

| voltage             | Ports 1 to 3                                            |     |                             | _                     | _   | 1.0                        | V    | $\begin{split} I_{\text{OL}} &= 5 \text{ mA} \\ (V_{\text{CC}} < 4.0 \text{ V}), \\ I_{\text{OL}} &= 10 \text{ mA} \\ (4.0 \text{ V} \leq V_{\text{CC}} \leq \\ 5.5 \text{ V}) \end{split}$ |

Conditions\*<sup>7</sup>:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, \text{ AV}_{CC}$ \*<sup>1</sup> = 2.7 V to 5.5 V,  $V_{SS} = \text{AV}_{SS}$ \*<sup>1</sup> = 0 V,  $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications)

| Item                                    |                             |     | Symbol           | Min | Тур  | Max  | Unit | Test Conditions                                        |

|-----------------------------------------|-----------------------------|-----|------------------|-----|------|------|------|--------------------------------------------------------|

| Input                                   | RES                         |     | I <sub>in</sub>  | _   | _    | 10.0 | μΑ   | $V_{in} = 0.5 \text{ to}$                              |

| leakage<br>current                      | STBY, NMI, MD1<br>MD0       | ,   | _                | _   | _    | 1.0  | μΑ   | ¯ V <sub>cc</sub> – 0.5 V                              |

|                                         | Port 7                      |     | _                | _   | _    | 1.0  | μА   | $V_{in} = 0.5 \text{ to}$<br>$AV_{CC} - 0.5 \text{ V}$ |

| Three-state leakage current (off state) | Ports 1 to 6<br>Ports 8, 9  |     | I <sub>TSI</sub> | _   | _    | 1.0  | μА   | $V_{in} = 0.5 \text{ to}$<br>$V_{CC} - 0.5 \text{ V}$  |

| Input pull-<br>up MOS                   | Ports 1 to 3                |     | -I <sub>P</sub>  | 10  | _    | 150  | μΑ   | $V_{in} = 0 \text{ V},$ $V_{CC} = 2.7 \text{ V to}$    |

| current                                 | Port 6                      |     | <del>_</del>     | 30  | _    | 250  | μΑ   | _ 3.6 V                                                |

| Input capacitance                       | RES                         | (4) | C <sub>in</sub>  | _   | _    | 80   | pF   | $V_{in} = 0 V,$<br>f = 1 MHz,                          |

|                                         | NMI                         |     |                  | _   | _    | 50   | pF   | $T_{a} = 25^{\circ}C$                                  |

|                                         | P52, P97,<br>P42, P86       |     |                  | _   |      | 20   | pF   | _                                                      |

|                                         | Input pins except (4) above |     |                  | _   |      | 15   | pF   | _                                                      |

| Current dissipation*8                   | Normal operation            |     | I <sub>cc</sub>  | _   | 45   | 60   | mA   | f = 10 MHz,<br>H8S/2134 Series                         |

|                                         |                             |     |                  | _   | 50   | 70   | mA   | f = 10 MHz,<br>H8S/2138 Series                         |

|                                         | Sleep mode                  |     | _                | _   | 35   | 50   | mA   | f = 10 MHz,<br>H8S/2134 Series                         |

|                                         |                             |     |                  | _   | 40   | 60   | mA   | f = 10 MHz,<br>H8S/2138 Series                         |

|                                         | Standby mode*9              |     | <del>_</del>     | _   | 0.01 | 5.0  | μΑ   | $T_a \le 50^{\circ}C$                                  |

|                                         |                             |     |                  | _   | _    | 20.0 | μΑ   | 50°C < T <sub>a</sub>                                  |

| Analog<br>power                         | During A/D, D/A conversion  |     | Al <sub>cc</sub> | _   | 3.2  | 7.0  | mA   |                                                        |

| supply<br>current                       | Idle                        |     | _                | _   | 0.01 | 5.0  | μΑ   | AV <sub>cc</sub> = 2.0 V to 5.5 V                      |

Conditions\*<sup>7</sup>:

$$V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, AV_{CC}*^{1} = 2.7 \text{ V to } 5.5 \text{ V}, V_{SS} = AV_{SS}*^{1} = 0 \text{ V},$$

$T_a = -20 \text{ to } +75^{\circ}\text{C} \text{ (regular specifications)}$

| Item                          | Symbol    | Min | Тур | Max | Unit | <b>Test Conditions</b> |

|-------------------------------|-----------|-----|-----|-----|------|------------------------|

| Analog power supply voltage*1 | $AV_CC$   | 2.7 | _   | 5.5 | V    | Operating              |

|                               |           | 2.0 | _   | 5.5 | V    | Idle/not used          |

| RAM standby voltage           | $V_{RAM}$ | 2.0 | _   | _   | V    |                        |

Notes: 1. Do not leave the AVCC, and AVSS pins open even if the A/D converter and D/A converter are not used.

Even if the A/D converter and D/A converter are not used, apply a value in the range 2.0 V to 5.5 V to AVCC by connection to the power supply ( $V_{CC}$ ), or some other method.

- 2. P67 to P60 include supporting module inputs multiplexed on those pins.

- 3. IRQ2 includes the ADTRG signal multiplexed on that pin.

- P52/SCK0/SCL0 and P97/SDA0 are NMOS push-pull outputs.

An external pull-up resistor is necessary to provide high-level output from SCL0 and SDA0 (ICE = 1).

P52/SCK0 and P97 (ICE = 0) high levels are driven by NMOS.

- 5. When ICE = 0. Low-level output when the bus drive function is selected is determined separately.

- 6. The upper limit of the port 6 applied voltage is  $V_{cc}$  + 0.3 V when CIN input is not selected, and the lower of  $V_{cc}$  + 0.3 V and  $AV_{cc}$  + 0.3 V when CIN input is selected. When a pin is in output mode, the output voltage is equivalent to the applied voltage.

- 7. The operating supply voltage range specification for the F-ZTAT (low-voltage) version is under investigation. Ranges of  $V_{\rm CC}$  = 3.0 to 3.6 V and  $T_{\rm a}$  = 0 to +75°C are planned for flash memory programming/erasing.

- 8. Current dissipation values are for  $V_{IH}$  min =  $V_{CC} 0.5$  V and  $V_{IL}$  max = 0.5 V with all output pins unloaded and the on-chip pull-up MOSs in the off state.

- 9. The values are for  $V_{RAM} \le V_{CC} < 2.7 \text{ V}$ ,  $V_{IH} \text{ min} = V_{CC} \times 0.9$ , and  $V_{IL} \text{ max} = 0.3 \text{ V}$ .

Conditions:  $V_{CC} = 4.0 \text{ V}$  to 5.5 V,  $V_{SS} = 0 \text{ V}$ ,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

| Item                                      |                                               | Symbol                 | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------------------------------------|------------------------|-----|-----|-----|------|

| Permissible output low current (per pin)  | SCL1, SCL0, SDA1,<br>SDA0                     | I <sub>OL</sub>        | _   | _   | 20  | mA   |

|                                           | Ports 1, 2, 3                                 | _                      | _   | _   | 10  | mA   |

|                                           | Other output pins                             | _                      | _   | _   | 2   | mA   |

| Permissible output                        | Total of ports 1, 2, and 3                    | $\sum$ I <sub>OL</sub> | _   | _   | 80  | mA   |

| low current (total)                       | Total of all output pins, including the above | _                      | _   | _   | 120 | mA   |

| Permissible output high current (per pin) | All output pins                               | -I <sub>OH</sub>       | _   | _   | 2   | mA   |

| Permissible output high current (total)   | Total of all output pins                      | $\Sigma - I_{OH}$      | _   | _   | 40  | mA   |

Notes: 1. To protect chip reliability, do not exceed the output current values in table 24.3.

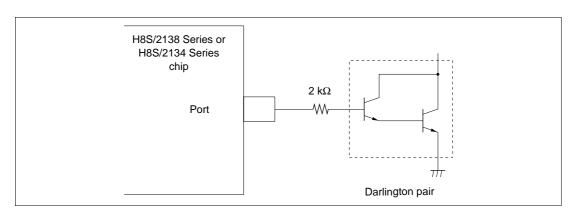

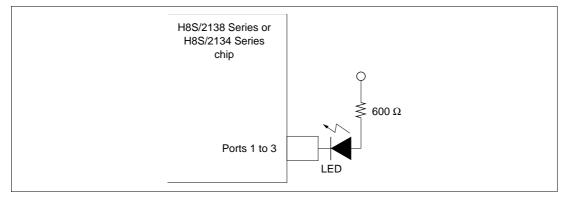

2. When driving a Darlington pair or LED, always insert a current-limiting resistor in the output line, as show in figures 24.1 and 24.2.

#### **Table 24.3 Permissible Output Currents (cont)**

- Preliminary -

Conditions:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications)

| Item                                      |                                               | Symbol                  | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------------------------------------|-------------------------|-----|-----|-----|------|

| Permissible output low current (per pin)  | SCL1, SCL0, SDA1,<br>SDA0                     | I <sub>OL</sub>         | _   | _   | 10  | mA   |

|                                           | Ports 1, 2, 3                                 | _                       | _   | _   | 2   | mA   |

|                                           | Other output pins                             | _                       | _   | _   | 1   | mA   |

| Permissible output                        | Total of ports 1, 2, and 3                    | $\sum$ I <sub>OL</sub>  | _   | _   | 40  | mA   |

| low current (total)                       | Total of all output pins, including the above | _                       | _   | _   | 60  | mA   |

| Permissible output high current (per pin) | All output pins                               | <b>-I</b> <sub>OH</sub> | _   | _   | 2   | mA   |

| Permissible output high current (total)   | Total of all output pins                      | $\Sigma - I_{OH}$       | _   | _   | 30  | mA   |

Notes: 1. To protect chip reliability, do not exceed the output current values in table 24.3.

2. When driving a Darlington pair or LED, always insert a current-limiting resistor in the output line, as show in figures 24.1 and 24.2.

Conditions:  $V_{CC} = 2.7 \text{ V}$  to 5.5 V,  $V_{SS} = 0 \text{ V}$ ,  $Ta = -20 \text{ to } +75^{\circ}\text{C}$

Applicable Pins: SCL1, SCL0, SDA1, SDA0 (bus drive function selected)

| Item                                    | Symbol                      | Min                        | Тур | Max                        | Unit        | Test Conditions                                                           |

|-----------------------------------------|-----------------------------|----------------------------|-----|----------------------------|-------------|---------------------------------------------------------------------------|

| Schmitt trigger input voltage           | V <sub>T</sub>              | $V_{cc} \times 0.3$        | _   | _                          | V           | $V_{cc} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

|                                         | V <sub>T</sub> <sup>+</sup> | _                          | _   | $V_{\text{cc}} \times 0.7$ |             | $V_{cc} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

|                                         | $V_T^+ - V_T^-$             | $V_{\text{CC}}\times 0.05$ | _   | _                          | <del></del> | $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

| Input high voltage                      | $V_{IH}$                    | $V_{\text{CC}}\times 0.7$  | _   | $V_{cc}$ + 0.5             | V           | $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

| Input low voltage                       | $V_{IL}$                    | -0.5                       | _   | $V_{\text{CC}}\times 0.3$  |             | $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

| Output low voltage                      | $V_{OL}$                    | _                          | _   | 0.8                        | V           | $I_{OL} = 16 \text{ mA},$<br>$V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$   |

|                                         |                             | _                          | _   | 0.5                        |             | $I_{OL} = 8 \text{ mA}$                                                   |

|                                         |                             | _                          | _   | 0.4                        | <del></del> | I <sub>OL</sub> = 3 mA                                                    |

| Input capacitance                       | $C_in$                      | _                          | _   | 20                         | pF          | $V_{in} = 0 \text{ V, } f = 1 \text{ MHz,}$<br>$T_a = 25^{\circ}\text{C}$ |

| Three-state leakage current (off state) | I <sub>TSI</sub>            | _                          | _   | 1.0                        | μΑ          | $V_{in} = 0.5 \text{ to } V_{CC} - 0.5 \text{ V}$                         |

| SCL, SDA output fall time               | t <sub>Of</sub>             | 20 + 0.1Cb                 | _   | 250                        | ns          | $V_{cc} = 2.7 \text{ V to } 5.5 \text{ V}$                                |

Figure 24.1 Darlington Pair Drive Circuit (Example)

Figure 24.2 LED Drive Circuit (Example)

### 24.3 AC Characteristics

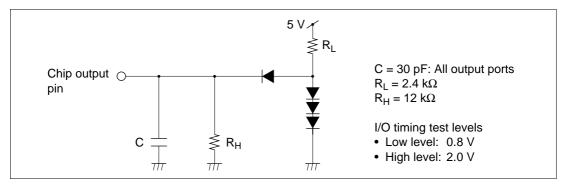

Figure 24.3 shows the test conditions for the AC characteristics.

Figure 24.3 Output Load Circuit

#### 24.3.1 Clock Timing

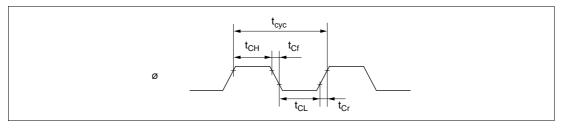

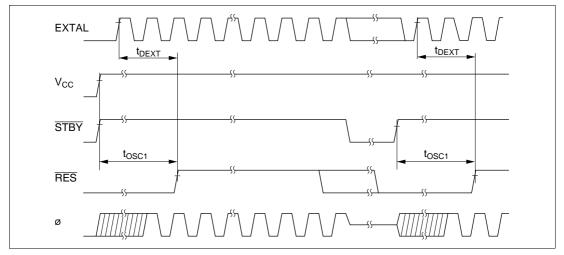

Table 24.5 shows the clock timing. The clock timing specified here covers clock (ø) output and clock pulse generator (crystal) and external clock input (EXTAL pin) oscillation settling times. For details of external clock input (EXTAL pin and EXCL pin) timing, see section 22, Clock Pulse Generator.

#### Table 24.5 Clock Timing

- Preliminary -

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{V}, V_{SS} = 0 \text{ V}, \emptyset = 2 \text{ MHz to maximum operating frequency},$   $T_a = -20 \text{ to } +75^{\circ}\text{C (regular specifications)},$   $T_a = -40 \text{ to } +85^{\circ}\text{C (wide-range specifications)}$

Condition C:  $V_{CC} = 2.7 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications)

|                                                         |                   |     | dition A |      | MHz |     | dition C |      |                            |

|---------------------------------------------------------|-------------------|-----|----------|------|-----|-----|----------|------|----------------------------|

| Item                                                    | Symbol            | Min | Max      | Min  | Max | Min | Max      | Unit | Test<br>Conditions         |

| Clock cycle time                                        | t <sub>cyc</sub>  | 50  | 500      | 62.5 | 500 | 100 | 500      | ns   | Figure 24.4                |

| Clock high pulse width                                  | t <sub>CH</sub>   | 17  | _        | 20   | _   | 30  | _        | ns   | Figure 24.4                |

| Clock low pulse width                                   | t <sub>CL</sub>   | 17  | _        | 20   | _   | 30  | _        | ns   | _                          |

| Clock rise time                                         | t <sub>Cr</sub>   | _   | 8        | _    | 10  | _   | 20       | ns   | _                          |

| Clock fall time                                         | t <sub>Cf</sub>   | _   | 8        | _    | 10  | _   | 20       | ns   | <del></del>                |

| Oscillation settling time at reset (crystal)            | t <sub>OSC1</sub> | 10  | _        | 10   | _   | 20  | _        | ms   | Figure 24.5<br>Figure 24.6 |

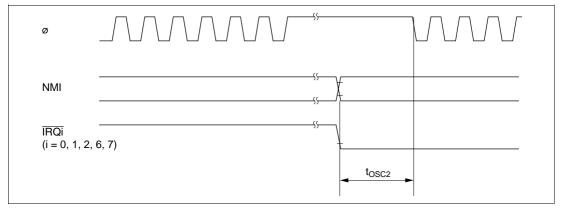

| Oscillation settling time in software standby (crystal) | t <sub>osc2</sub> | 8   | _        | 8    | _   | 8   | _        | ms   | _                          |

| External clock output stabilization delay time          | t <sub>DEXT</sub> | 500 | _        | 500  | _   | 500 | _        | μs   |                            |

Figure 24.4 System Clock Timing

Figure 24.5 Oscillation Settling Timing

Figure 24.6 Oscillation Setting Timing (Exiting Software Standby Mode)

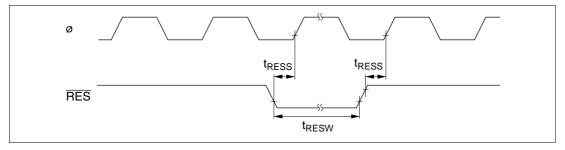

#### 24.3.2 Control Signal Timing

Table 24.6 shows the control signal timing. The only external interrupts that can operate on the subclock ( $\phi = 32.768 \text{ kHz}$ ) are NMI and IRQ0, IRQ1, IRQ2, IRQ6, and IRQ7.

#### **Table 24.6 Control Signal Timing**

- Preliminary -

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz}$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{V}, V_{SS} = 0 \text{ V}, \emptyset = 32.768 \text{ kHz}, 2 \text{ MHz to maximum operating}$  frequency,  $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85 ^{\circ}\text{C}$  (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz}$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications)

|                                                                            |                   | Conc | lition A | Cond | lition B | Cond | lition C |               |             |

|----------------------------------------------------------------------------|-------------------|------|----------|------|----------|------|----------|---------------|-------------|

|                                                                            |                   | 20   | MHz      | 16   | MHz      | 10   | MHz      |               | Test        |

| Item                                                                       | Symbol            | Min  | Max      | Min  | Max      | Min  | Max      | Unit          | Conditions  |

| RES setup time                                                             | t <sub>RESS</sub> | 200  | _        | 200  | _        | 300  | _        | ns            | Figure 24.7 |

| RES pulse width                                                            | $t_{RESW}$        | 20   | _        | 20   | _        | 20   | _        | $t_{\rm cyc}$ |             |

| NMI setup time<br>(NMI)                                                    | t <sub>NMIS</sub> | 150  | _        | 150  | _        | 250  | _        | ns            | Figure 24.8 |

| NMI hold time<br>(NMI)                                                     | t <sub>nmih</sub> | 10   | _        | 10   | _        | 10   | _        |               |             |

| NMI pulse width (exiting software standby mode)                            | t <sub>NMIW</sub> | 200  | _        | 200  | _        | 200  | _        | ns            | _           |

| IRQ setup time (IRQ7 to IRQ0)                                              | t <sub>IRQS</sub> | 150  | _        | 150  | _        | 250  | _        | ns            | _           |

| IRQ hold time<br>(IRQ7 to IRQ0)                                            | t <sub>IRQH</sub> | 10   | _        | 10   | _        | 10   | _        | ns            | _           |

| IRQ pulse width (IRQ7, IRQ6, IRQ2 to IRQ0) (exiting software standby mode) | t <sub>IROW</sub> | 200  | _        | 200  | _        | 200  | _        | ns            |             |

Figure 24.7 Reset Input Timing

Figure 24.8 Interrupt Input Timing

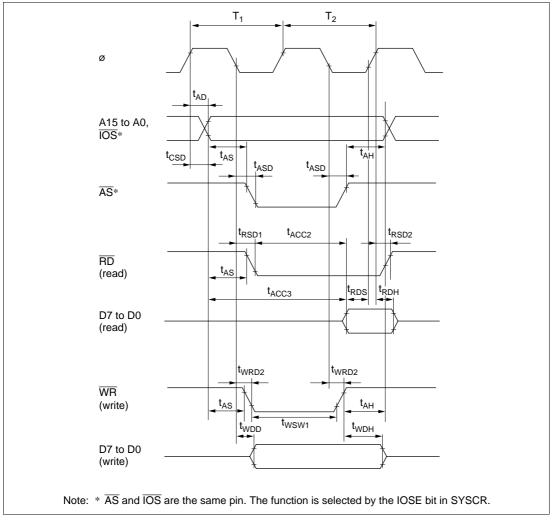

#### 24.3.3 Bus Timing

Table 24.7 shows the bus timing. Operation in external expansion mode is not guaranteed when operating on the subclock ( $\phi = 32.768 \text{ kHz}$ ).

#### **Table 24.7 Bus Timing**

- Preliminary -

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),

$T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),

$T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications)

|                         |                   | Cond                           | ition A                        | Cond                           | ition B                        | Cond                           | ition C                        |      |                   |

|-------------------------|-------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------|-------------------|

|                         |                   | 20                             | MHz                            | 16                             | MHz                            | 10                             | MHz                            |      | Test              |

| Item                    | Symbol            | Min                            | Max                            | Min                            | Max                            | Min                            | Max                            | Unit |                   |

| Address<br>delay time   | t <sub>AD</sub>   | _                              | 20                             | _                              | 30                             | _                              | 40                             | ns   | Figure 24.9<br>to |

| Address setup time      | t <sub>AS</sub>   | 0.5 ×<br>t <sub>cyc</sub> – 15 | _                              | 0.5 ×<br>t <sub>cyc</sub> - 20 | _                              | 0.5 ×<br>t <sub>cyc</sub> - 30 | _                              | ns   | figure 24.13      |

| Address<br>hold time    | t <sub>AH</sub>   | 0.5 ×<br>t <sub>cyc</sub> – 10 | _                              | 0.5 ×<br>t <sub>cyc</sub> – 15 | _                              | $0.5 \times t_{\rm cyc} - 20$  | _                              | ns   |                   |

| CS delay time (IOS)     | t <sub>CSD</sub>  | _                              | 20                             | _                              | 30                             | _                              | 40                             | ns   | _                 |

| AS delay time           | t <sub>ASD</sub>  | _                              | 30                             | _                              | 45                             | _                              | 60                             | ns   | _                 |

| RD delay time 1         | t <sub>RSD1</sub> | _                              | 30                             | _                              | 45                             | _                              | 60                             | ns   | _                 |

| RD delay time 2         | t <sub>RSD2</sub> | _                              | 30                             | _                              | 45                             | _                              | 60                             | ns   | _                 |

| Read data setup time    | t <sub>RDS</sub>  | 15                             | _                              | 20                             | _                              | 35                             | _                              | ns   | _                 |

| Read data hold time     | t <sub>RDH</sub>  | 0                              | _                              | 0                              | _                              | 0                              | _                              | ns   | _                 |

| Read data access time 1 | t <sub>ACC1</sub> | _                              | 1.0 ×<br>t <sub>cyc</sub> - 30 | _                              | 1.0 ×<br>t <sub>cyc</sub> - 40 | _                              | 1.0 ×<br>t <sub>cyc</sub> - 60 | ns   | _                 |

| Read data access time 2 | t <sub>ACC2</sub> |                                | $1.5 \times t_{\rm cyc} - 25$  |                                | $1.5 \times t_{\rm cyc} - 35$  |                                | $1.5 \times t_{\rm cyc} - 50$  | ns   |                   |

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20$  to +75°C (regular specifications),  $T_a = -40$  to +85°C (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C} \text{ (regular specifications)}$

|                         |                   | Cond                           | lition A                            | Cond                           | lition B                            | Cond                          | lition C                         |      |                |

|-------------------------|-------------------|--------------------------------|-------------------------------------|--------------------------------|-------------------------------------|-------------------------------|----------------------------------|------|----------------|

|                         |                   | 20                             | MHz                                 | 16                             | MHz                                 | 10                            | MHz                              |      | Test           |

| Item                    | Symbol            | Min                            | Max                                 | Min                            | Max                                 | Min                           | Max                              | Unit |                |

| Read data access time 3 | t <sub>ACC3</sub> | _                              | $2.0 \times t_{\rm cyc} - 30$       | _                              | 2.0 × t <sub>cyc</sub> - 40         | _                             | $2.0 \times t_{\text{cyc}} - 60$ | ns   | Figure 24.9 to |

| Read data access time 4 | t <sub>ACC4</sub> | -                              | $2.5 \times t_{\rm cyc} - 25$       | _                              | $2.5 \times t_{\rm cyc} - 35$       | -                             | $2.5 \times t_{\rm cyc} - 50$    | ns   | figure 24.13   |

| Read data access time 5 | t <sub>ACC5</sub> | _                              | $3.0 \times \\ t_{\text{cyc}} - 30$ | _                              | $3.0 \times \\ t_{\text{cyc}} - 40$ | _                             | $3.0 \times t_{\rm cyc} - 60$    | ns   |                |

| WR delay time 1         | t <sub>WRD1</sub> | _                              | 30                                  | _                              | 45                                  | _                             | 60                               | ns   |                |

| WR delay time 2         | t <sub>WRD2</sub> | -                              | 30                                  | _                              | 45                                  | _                             | 60                               | ns   | _              |

| WR pulse width 1        | t <sub>wsw1</sub> | 1.0 ×<br>t <sub>cyc</sub> - 20 | _                                   | 1.0 ×<br>t <sub>cyc</sub> - 30 | _                                   | 1.0×<br>t <sub>cyc</sub> - 40 | _                                | ns   | _              |

| WR pulse<br>width 2     | t <sub>wsw2</sub> | 1.5 × t <sub>cyc</sub> – 20    | _                                   | 1.5 × t <sub>cyc</sub> - 30    | _                                   | 1.5 × t <sub>cyc</sub> – 40   |                                  | ns   | _              |

| Write data delay time   | t <sub>WDD</sub>  | _                              | 30                                  | _                              | 45                                  | _                             | 60                               | ns   | _              |

| Write data setup time   | t <sub>wds</sub>  | 0                              | _                                   | 0                              | _                                   | 0                             | _                                | ns   | _              |

| Write data hold time    | t <sub>WDH</sub>  | 10                             | _                                   | 15                             | _                                   | 20                            | _                                | ns   | _              |

| WAIT setup time         | t <sub>WTS</sub>  | 30                             | _                                   | 45                             | _                                   | 60                            | _                                | ns   | _              |

| WAIT hold time          | t <sub>WTH</sub>  | 5                              | _                                   | 5                              | _                                   | 10                            | _                                | ns   |                |

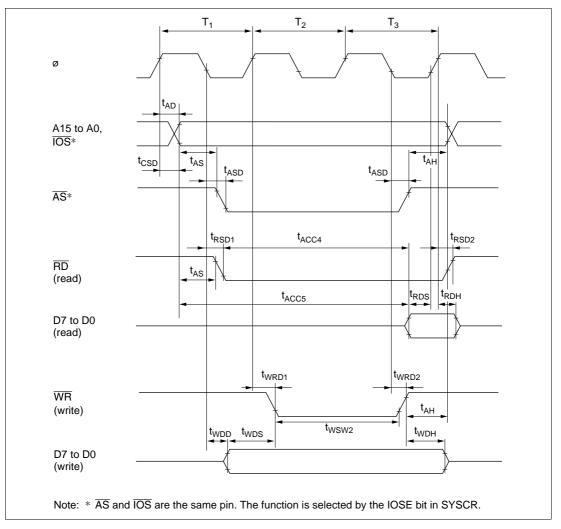

Figure 24.9 Basic Bus Timing (Two-State Access)

Figure 24.10 Basic Bus Timing (Three-State Access)

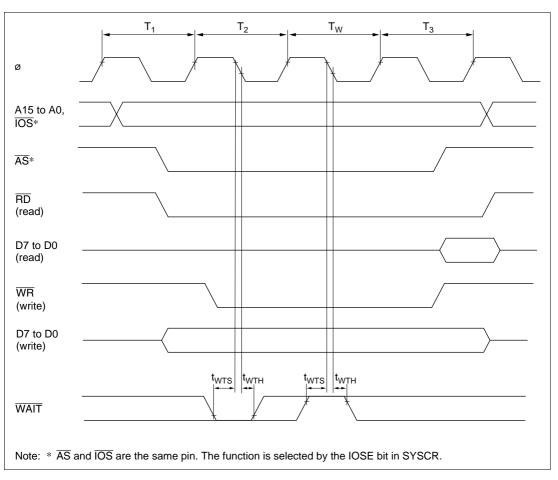

Figure 24.11 Basic Bus Timing (Three-State Access with One Wait State)

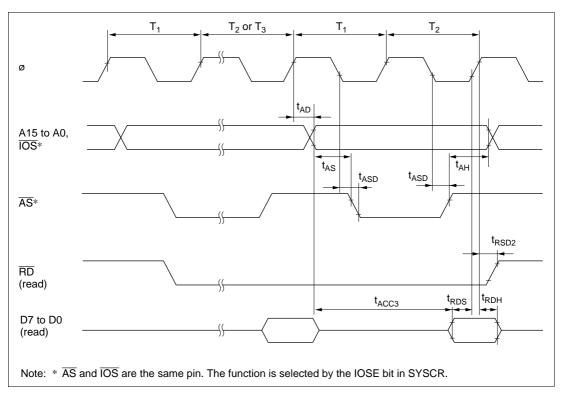

Figure 24.12 Burst ROM Access Timing (Two-State Access)

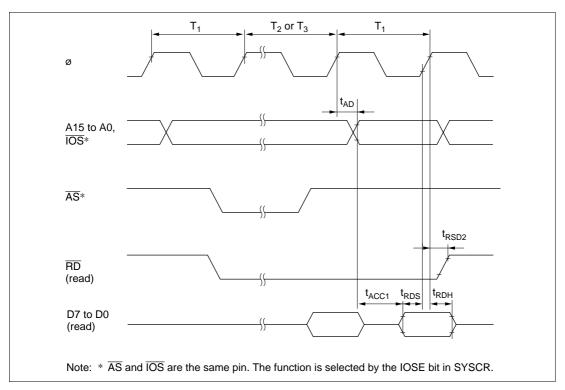

Figure 24.13 Burst ROM Access Timing (One-State Access)

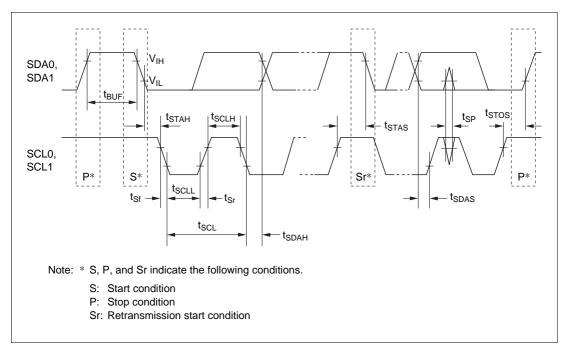

#### 24.3.4 Timing of On-Chip Supporting Modules

Tables 24.8 and 24.9 show the on-chip supporting module timing. The only on-chip supporting modules that can operate in subclock operation ( $\emptyset = 32.768 \text{ kHz}$ ) are the I/O ports, external interrupts (NMI and IRQ0, 1, 2, 6, and 7), the watchdog timer, and the 8-bit timer (channels 0 and 1).

#### **Table 24.8 Timing of On-Chip Supporting Modules (1)**

- Preliminary -

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz}^*$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \emptyset = 32.768 \text{ kHz*}, 2 \text{ MHz to maximum operating}$  frequency,  $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85 ^{\circ}\text{C}$  (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz*}$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications)

|              |                      |                |                    | Cond | dition A | Cond | dition B | Cond | dition C |                  |                 |

|--------------|----------------------|----------------|--------------------|------|----------|------|----------|------|----------|------------------|-----------------|

|              |                      |                |                    | 20   | MHz      | 16   | MHz      | 10   | MHz      |                  | Test            |

| Item         |                      |                | Symbol             | Min  | Max      | Min  | Max      | Min  | Max      | Unit             | Conditions      |

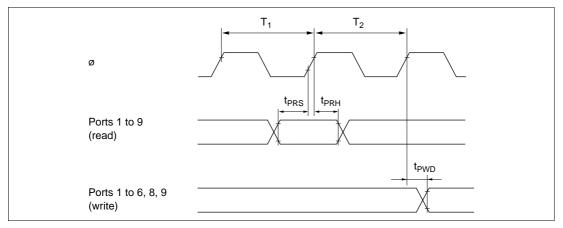

| I/O<br>ports | Output d             | ata delay      | t <sub>PWD</sub>   | _    | 50       | _    | 50       | _    | 100      | ns               | Figure<br>24.14 |

|              | Input dat            | ta setup       | t <sub>PRS</sub>   | 30   | _        | 30   | _        | 50   | _        |                  |                 |

|              | Input data hold time |                | t <sub>PRH</sub>   | 30   | _        | 30   | _        | 50   | _        |                  |                 |

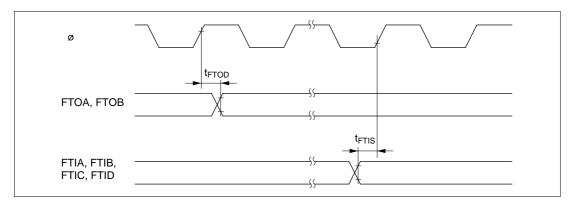

| FRT          | Timer ou             | ıtput delay    | $t_{\text{FTOD}}$  | -    | 50       | _    | 50       | -    | 100      | ns               | Figure<br>24.15 |

|              | Timer in time        | out setup      | t <sub>FTIS</sub>  | 30   | _        | 30   | _        | 50   | _        |                  |                 |

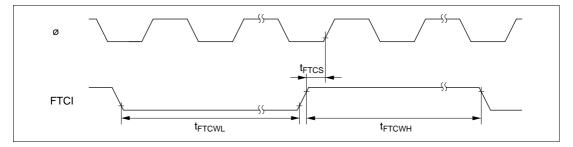

|              | Timer clo            |                | t <sub>FTCS</sub>  | 30   | _        | 30   | _        | 50   | _        |                  | Figure 24.16    |

|              | Timer clock          | Single<br>edge | t <sub>FTCWH</sub> | 1.5  | _        | 1.5  | _        | 1.5  | _        | t <sub>cyc</sub> | _               |

|              | pulse<br>width       | Both<br>edges  | t <sub>FTCWL</sub> | 2.5  | _        | 2.5  | _        | 2.5  | _        |                  |                 |

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz}^*$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \emptyset = 32.768 \text{ kHz*}, 2 \text{ MHz to maximum operating}$  frequency,  $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85 ^{\circ}\text{C}$  (wide-range specifications)

$\label{eq:conditionC} \begin{array}{ll} \text{Condition C:} & V_{\text{CC}} = 2.7 \text{ V to 5.5V}, V_{\text{SS}} = 0 \text{ V}, \emptyset = 32.768 \text{ kHz*}, 2 \text{ MHz to maximum operating frequency}, T_{\text{a}} = -20 \text{ to } +75 ^{\circ}\text{C (regular specifications)} \end{array}$

|              |                   |                   |                    | Cond | dition A | Cond | dition B | Cond | dition C |                   |                 |

|--------------|-------------------|-------------------|--------------------|------|----------|------|----------|------|----------|-------------------|-----------------|

|              |                   |                   |                    | 20   | MHz      | 16   | MHz      | 10   | MHz      |                   | Test            |

| Item         |                   |                   | Symbol             | Min  | Max      | Min  | Max      | Min  | Max      | Unit              | Conditions      |

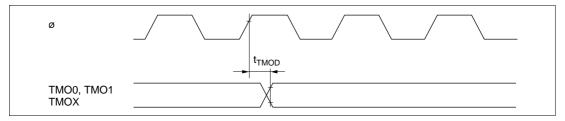

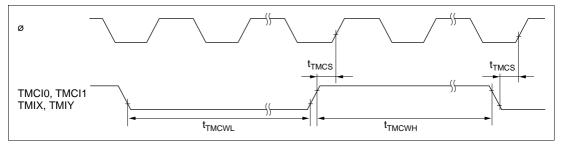

| TMR          | Timer o           |                   | t <sub>TMOD</sub>  | _    | 50       | _    | 50       | _    | 100      | ns                | Figure<br>24.17 |

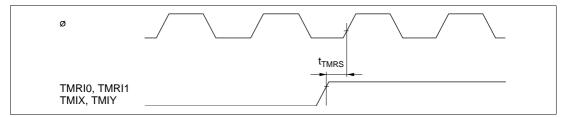

|              | Timer r           | eset input<br>me  | t <sub>TMRS</sub>  | 30   | _        | 30   | _        | 50   | _        |                   | Figure 24.19    |

|              | Timer o           | clock input<br>me | t <sub>TMCS</sub>  | 30   | _        | 30   | _        | 50   | _        |                   | Figure 24.18    |

|              | Timer clock       | Single edge       | t <sub>TMCWH</sub> | 1.5  | _        | 1.5  | _        | 1.5  | _        | t <sub>cyc</sub>  | _               |

|              | pulse<br>width    | Both edges        | t <sub>TMCWL</sub> | 2.5  | _        | 2.5  | _        | 2.5  | _        |                   |                 |

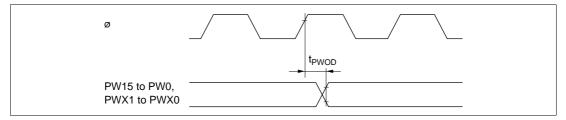

| PWM,<br>PWMX | Pulse o           | •                 | t <sub>PWOD</sub>  | _    | 50       | _    | 50       | _    | 100      | ns                | Figure<br>24.20 |

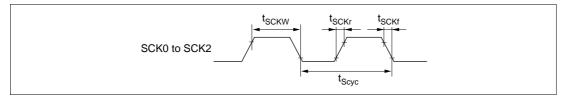

| SCI          | Input<br>clock    | Asynchro-<br>nous | t <sub>Scyc</sub>  | 4    | _        | 4    | _        | 4    | _        | t <sub>cyc</sub>  | Figure<br>24.21 |

|              | cycle             | Synchro-<br>nous  | _                  | 6    | _        | 6    | _        | 6    | _        |                   |                 |

|              | Input cl<br>width | ock pulse         | t <sub>SCKW</sub>  | 0.4  | 0.6      | 0.4  | 0.6      | 0.4  | 0.6      | t <sub>Scyc</sub> | _               |

|              | Input cl          | ock rise          | t <sub>SCKr</sub>  | _    | 1.5      | _    | 1.5      | _    | 1.5      | t <sub>cyc</sub>  | _               |

|              | Input cl          | ock fall          | t <sub>SCKf</sub>  | _    | 1.5      | _    | 1.5      | _    | 1.5      |                   |                 |

### Table 24.8 Timing of On-Chip Supporting Modules (1) (cont)

- Preliminary -

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz}^*$ , 2 MHz to maximum operating frequency,  $T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),

$T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 32.768 \text{ kHz*}$ , 2 MHz to maximum operating

frequency,  $T_a = -20$  to +75°C (regular specifications),

$T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \emptyset = 32.768 \text{ kHz*}, 2 \text{ MHz to maximum operating}$  frequency,  $T_a = -20 \text{ to } +75 ^{\circ}\text{C}$  (regular specifications)

|                  |                                            |                  | Cond | dition A | Cond | dition B | Cond | dition C |      |                 |

|------------------|--------------------------------------------|------------------|------|----------|------|----------|------|----------|------|-----------------|

|                  |                                            |                  | 20   | MHz      | 16   | MHz      | 10   | MHz      |      | Test            |

| Item             |                                            | Symbol           | Min  | Max      | Min  | Max      | Min  | Max      | Unit | Conditions      |

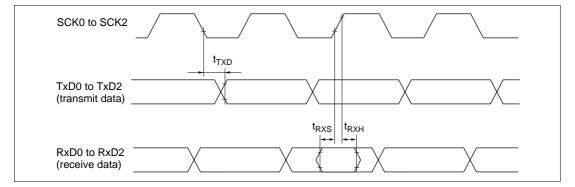

| SCI              | Transmit data delay time (synchronous)     | t <sub>TXD</sub> | _    | 50       | _    | 50       | _    | 100      | ns   | Figure<br>24.22 |

|                  | Receive data setup time (synchronous)      | t <sub>RXS</sub> | 50   | _        | 50   | _        | 100  | _        | ns   |                 |

|                  | Receive data<br>hold time<br>(synchronous) | t <sub>RXH</sub> | 50   | _        | 50   | _        | 100  | _        | ns   | -               |

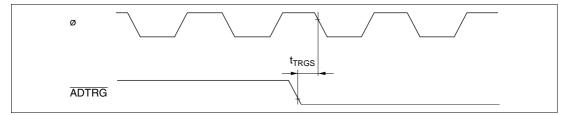

| A/D<br>converter | Trigger input setup time                   | t <sub>RGS</sub> | 30   | _        | 30   | _        | 50   | _        | ns   | Figure<br>24.23 |

Note: \* Only supporting modules that can be used in subclock operation

Figure 24.14 I/O Port Input/Output Timing

Figure 24.15 FRT Input/Output Timing

Figure 24.16 FRT Clock Input Timing

Figure 24.17 8-Bit Timer Output Timing

Figure 24.18 8-Bit Timer Clock Input Timing

Figure 24.19 8-Bit Timer Reset Input Timing

Figure 24.20 PWM, PWMX Output Timing

Figure 24.21 SCK Clock Input Timing

Figure 24.22 SCI Input/Output Timing (Synchronous Mode)

Figure 24.23 A/D Converter External Trigger Input Timing

Condition A:  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20 \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40 \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition B:  $V_{CC} = 4.0 \text{ V}$  to 5.5V,  $V_{SS} = 0 \text{ V}$ ,  $\emptyset = 2 \text{ MHz}$  to maximum operating frequency,

$T_a = -20$  to +75°C (regular specifications),  $T_a = -40$  to +85°C (wide-range specifications)

Condition C:  $V_{CC} = 2.7 \text{ V to } 5.5 \text{V}, V_{SS} = 0 \text{ V}, \emptyset = 2 \text{ MHz to maximum operating frequency},$   $T_a = -20 \text{ to } +75 ^{\circ}\text{C} \text{ (regular specifications)}$

|                 |                      |                              |                   | Conc | lition A | Conc | lition B | Conc | lition C |      |                 |

|-----------------|----------------------|------------------------------|-------------------|------|----------|------|----------|------|----------|------|-----------------|

|                 |                      |                              |                   | 20   | MHz      | 16   | MHz      | 10   | MHz      |      | Test            |

| Item            |                      |                              | Symbol            | Min  | Max      | Min  | Max      | Min  | Max      | Unit | Conditions      |

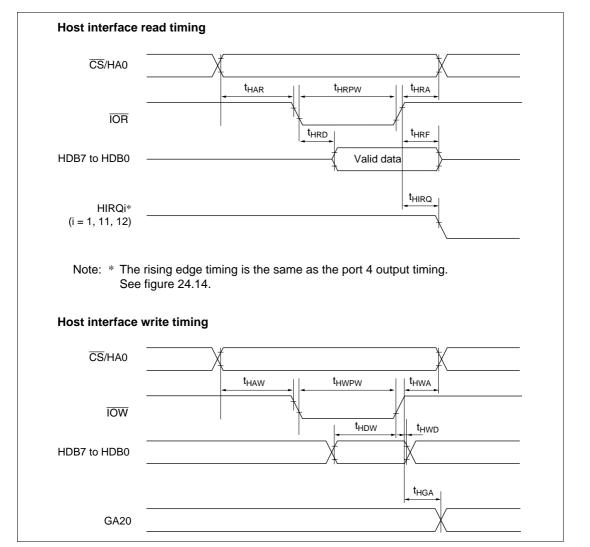

| HIF read cycle  | CS/HA<br>item        | 0 setup                      | t <sub>HAR</sub>  | 10   | _        | 10   | _        | 10   | _        | ns   | Figure<br>24.24 |

|                 | CS/HA                | 0 hold time                  | t <sub>HRA</sub>  | 10   | _        | 10   | _        | 10   | _        | ns   | <del>_</del>    |

|                 | ĪŌR pu               | lse width                    | t <sub>HRPW</sub> | 120  |          | 120  | _        | 220  | _        | ns   | =               |

|                 | HDB de               | elay time                    | t <sub>HRD</sub>  | _    | 100      | _    | 100      | _    | 200      | ns   | =               |

|                 | HDB h                | old time                     | t <sub>HRF</sub>  | 0    | 25       | 0    | 25       | 0    | 40       | ns   | =               |

|                 | HIRQ o               | delay time                   | t <sub>HIRQ</sub> | _    | 120      | _    | 120      | _    | 200      | ns   | =               |

| HIF write cycle | CS/HA<br>item        | 0 setup                      | t <sub>HAW</sub>  | 10   | _        | 10   | _        | 10   | _        | ns   | _               |

|                 | CS/HA                | 0 hold time                  | t <sub>HWA</sub>  | 10   |          | 10   | _        | 10   | _        | ns   | =               |

|                 | ĪŌW pu               | ulse width                   | t <sub>HWPW</sub> | 60   | _        | 60   | _        | 100  | _        | ns   | _               |

|                 | HDB<br>setup<br>time | Fast A20<br>gate not<br>used | t <sub>HDW</sub>  | 30   | _        | 30   | _        | 50   | _        | ns   | _               |

|                 |                      | Fast A20<br>gate used        | =                 | 45   | _        | 55   | _        | 85   | _        | ns   | _               |

|                 | HDB h                | old time                     | t <sub>HWD</sub>  | 15   | _        | 15   | _        | 25   | _        | ns   | _               |

|                 | GA20 d               | delay time                   | t <sub>HGA</sub>  | _    | 90       | _    | 90       | _    | 180      | ns   | _               |