# CA1524, CA2524 CA3524

**Regulating Pulse** Width Modulator

May 1992

#### **Features**

- Complete PWM Power Control Circuitry

- · Separate Outputs for Single-Ended or Push-Pull Operation

- Line and Load Regulation.......... 0.2% (Typ)

- Internal Reference Supply with 1% (Max) Oscillator Voltage Variation Over Reference Temperature Range

- · Standby Current of Less Than 10mA

- Frequency of Operation Beyond 100kHz

- Variable-Output Dead Time of 0.5μs to 5μs

- Low V<sub>CE(sat)</sub> Over the Temperature Range

## **Applications**

- Positive and Negative Regulated Supplies

- Dual-Output Regulators

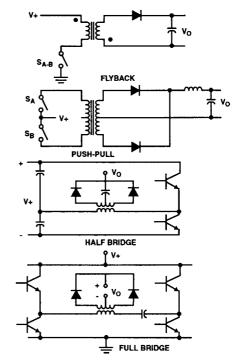

- Flyback Converters

- DC-DC Transformer-Coupled Regulating Converters

- Single-Ended DC-DC Converters

- Variable Power Supplies

## Description

The CA1524, CA2524, and CA3524 are silicon monolithic integrated circuits designed to provide all the control circuitry for use in a broad range of switching regulator circuits.

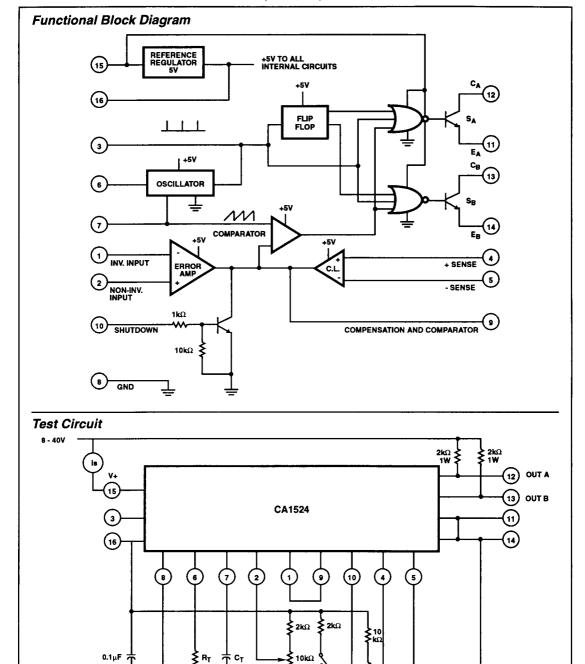

The CA1524, CA2524, and CA3524 have all the features of the industry types SG1524, SG2524, and SG3524, respectively. A block diagram of the CA1524 series is shown in Figure 1. The circuit includes a zener voltage reference, transconductance error amplifier, precision R-C oscillator, pulse-width modulator, pulse-steering flip-flop, dual alternating output switches, and current-limiting and shutdown circuitry. This device can be used for switching regulators of either polarity, transformer-coupled dc-dc converter, transformerless voltage doublers, dc-ac power inverters, highly efficient variable power supplies, and polarity converter, as well as other power-control applications.

## Ordering Information

| PART<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE             |

|----------------|----------------------|---------------------|

| CA1524E        | -55°C to +125°C      | 16 Lead Plastic DIP |

| CA1524F        | -55°C to +125°C      | 16 Lead Ceramic DIP |

| CA2524E        | 0°C to +70°C         | 16 Lead Plastic DIP |

| CA2524F        | 0°C to +70°C         | 16 Lead Ceramic DIP |

| CA3524E        | 0°C to +70°C         | 16 Lead Plastic DIP |

| CA3524F        | 0°C to +70°C         | 16 Lead Ceramic DIP |

| CA3524H        | 0°C to +70°C         | DICE                |

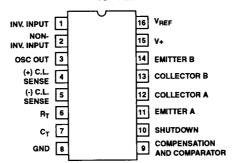

#### Pinout

#### 16 LEAD DUAL-IN-LINE PACKAGE TOP VIEW

**≨ 2k**Ω

1kΩ

## Specifications CA1524, CA2524, CA3524

## **Absolute Maximum Ratings**

| Output Current (Reference Regulator) | Up to T <sub>A</sub> = 25°C |

|--------------------------------------|-----------------------------|

| Oscillator Charging Current          | ·                           |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Characteristics T<sub>A</sub> = -55°C to +125°C for CA1524, 0°C to +70°C for the CA2524 and CA3524; V+ = 20V and f = 20kHz, Unless Otherwise Stated.

|                                                                        |                                             |       | LIMITS  |      |       |        |      |        |  |

|------------------------------------------------------------------------|---------------------------------------------|-------|---------|------|-------|--------|------|--------|--|

|                                                                        |                                             | CA1   | 524, CA | 2524 |       | CA3524 |      |        |  |

| PARAMETER                                                              | TEST CONDITIONS                             | MIN   | TYP     | MAX  | MIN   | TYP    | MAX  | UNITS  |  |

| REFERENCE SECTION                                                      |                                             |       |         |      |       |        |      |        |  |

| Output Voltage                                                         |                                             | 4.8   | 5       | 5.2  | 4.6   | 5      | 5.4  | ٧      |  |

| Line Regulation                                                        | V+ = 8 to 40V                               | -     | 10      | 20   | •     | 10     | 30   | mV     |  |

| Load Regulation                                                        | I <sub>L</sub> = 0 to 20mA                  | -     | 20      | 50   | -     | 20     | 50   | mV     |  |

| Ripple Rejection                                                       | f = 120Hz, T <sub>A</sub> = 25°C            | •     | 66      |      | •     | 66     | -    | db     |  |

| Short Circuit Current Limit                                            | V <sub>REF</sub> = 0, T <sub>A</sub> = 25°C |       | 100     |      | •     | 100    | -    | mA     |  |

| Temperature Stability                                                  | Over Operating Temperature Range            | •     | 0.3     | 1    | •     | 0.3    | 1    | %      |  |

| Long Term Stability                                                    | T <sub>A</sub> = 25°C                       | •     | 20      | -    |       | 20     | ·    | mV/khr |  |

| OSCILLATOR SECTION                                                     |                                             |       |         |      |       |        |      |        |  |

| Maximum Frequency                                                      | $C_T = 0.001 \mu F$ , $R_T = 2K\Omega$      |       | 300     | -    |       | 300    | -    | kHz    |  |

| Initial Accuracy                                                       | R <sub>T</sub> and C <sub>T</sub> Constant  | -     | 5       | -    | -     | 5      | -    | %      |  |

| Voltage Stability                                                      | V+ = 8 to 40V, T <sub>A</sub> = 25°C        |       | -       | 1    | •     | -      | 1    | %      |  |

| Temperature Stability                                                  | Over Operating Temperature Range            | -     | -       | 2    | •     | -      | 2    | %      |  |

| Output Amplitude                                                       | Terminal 3, T <sub>A</sub> = 25°C           | -     | 3.5     | -    | •     | 3.5    | -    | ٧      |  |

| Output Pulse Width (Pin 3)                                             | $C_T = 0.01 \mu F$ , $T_A = 25^{\circ}C$    |       | 0.5     | -    | •     | 0.5    | -    | μs     |  |

| Ramp Voltage Low (Note 1)                                              | Pin 7                                       |       | 0.6     | -    | •     | 0.6    |      | V      |  |

| Ramp Voltage High (Note 1)                                             | Pin 7                                       | -     | 3.5     | -    | •     | 3.5    | -    | V      |  |

| Capacitor Charging Current Range                                       | Pin 7 (5-2 V <sub>BE</sub> )/R <sub>T</sub> | 0.03  | -       | 2    | 0.03  |        | 2    | mA     |  |

| Timing Resistance Range                                                | Pin 6                                       | 1.8   | -       | 120  | 1.8   | ·      | 120  | kΩ     |  |

| Charging Capacitor Range                                               | Pin 7                                       | 0.001 | -       | 0.1  | 0.001 | -      | 0.1  | μF     |  |

| Dead Time Expansion Capacitor on Pin 3 (when a small osc. cap is used) | Pin 3                                       | 100   | -       | 1000 | 100   |        | 1000 | pF     |  |

| ERROR AMPLIFIER SECTION                                                |                                             | -     |         |      |       |        | -    |        |  |

| Input Offset Voltage                                                   | V <sub>CM</sub> = 2.5V                      | -     | 0.5     | 5    | -     | 2      | 10   | mV     |  |

| Input Bias Current                                                     | V <sub>CM</sub> = 2.5V                      |       | 1       | 10   | -     | 1      | 10   | μА     |  |

| Open Loop Voltage Gain                                                 |                                             | 72    | 80      | -    | 60    | 80     | -    | dB     |  |

| Common Mode Voltage                                                    | T <sub>A</sub> = 25°C                       | 1.8   | -       | 3.4  | 1.8   | -      | 3.4  | ٧      |  |

| Common Mode Rejection Ratio                                            | T <sub>A</sub> = 25°C                       | -     | 70      | -    |       | 70     | -    | dB     |  |

| Small Signal Bandwidth                                                 | A <sub>V</sub> = 0dB, T <sub>A</sub> = 25°C |       | 3       | -    |       | 3      | -    | MHz    |  |

| Output Voltage                                                         | T <sub>A</sub> = 25°C                       | 0.5   |         | 3.8  | 0.5   | -      | 3.8  | ٧      |  |

Electrical Characteristics T<sub>A</sub> = -55°C to +125°C for CA1524, 0°C to +70°C for the CA2524 and CA3524; V+ = 20V and f = 20kHz, Unless Otherwise Stated. (Continued)

|                                                | LIMITS                                                                            |     |                |     |        |     |     |       |

|------------------------------------------------|-----------------------------------------------------------------------------------|-----|----------------|-----|--------|-----|-----|-------|

|                                                |                                                                                   | CA1 | CA1524, CA2524 |     | CA3524 |     |     | İ     |

| PARAMETER                                      | TEST CONDITIONS                                                                   | MIN | TYP            | MAX | MIN    | TYP | MAX | UNITS |

| Amplifier Pole                                 | -                                                                                 | -   | 250            | -   | -      | 250 | -   | Hz    |

| Pin 9 Shutdown Current                         | External Sink                                                                     | -   | 200            | -   | -      | 200 | -   | μА    |

| COMPARATOR SECTION                             |                                                                                   |     |                |     |        | -   |     |       |

| Duty Cycle                                     | % Each Output On                                                                  | 0   | - "            | 45  | 0      | -   | 45  | %     |

| Input Threshold                                | Zero Duty Cycle                                                                   | -   | 1              | -   | •      | 1   | -   | ٧     |

| Input Threshold                                | Max. Duty Cycle                                                                   | -   | 3.5            | -   | -      | 3.5 | -   | ٧     |

| Input Bias Current                             |                                                                                   | -   | 1              | -   | -      | 1   | -   | μА    |

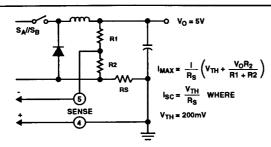

| CURRENT LIMITING SECTION                       |                                                                                   |     |                |     |        |     |     |       |

| Sense voltage for 25% Output Duty<br>Cycle     | Terminal 9 = 2V with Error<br>Amplifier Set for Max Out,<br>T <sub>A</sub> = 25°C | 190 | 200            | 210 | 180    | 200 | 220 | mV    |

| Sense Voltage T.C.                             |                                                                                   | -   | 0.2            | -   | -      | 0.2 | -   | mV/°C |

| Common Mode Voltage                            |                                                                                   | -1  | -              | +1  | -1     | -   | +1  | ٧     |

| Rolloff Pole of R51 C3 + Q64                   |                                                                                   | -   | 300            | -   | -      | 300 | -   | Hz    |

| OUTPUT SECTION (EACH OUTUT)                    |                                                                                   | _   |                |     |        | -   |     |       |

| Collector-Emitter Voltage                      |                                                                                   | 40  | -              | -   | 40     | -   | -   | ٧     |

| Collector Leakage Current                      | V <sub>CE</sub> = 40V                                                             |     | 0.1            | 50  |        | 0.1 | 50  | μА    |

| Saturation Voltage                             | V+ = 40V, I <sub>C</sub> = 50mA                                                   | T - | 0.8            | 2   | -      | 0.8 | 2   | ٧     |

| Emitter Output Voltage                         | V+ = 20V                                                                          | 17  | 18             | -   | 17     | 18  | -   | ٧     |

| Rise Time                                      | $R_C = 2K\Omega$ , $T_A = 25^{\circ}C$                                            | -   | 0.2            | -   | -      | 0.2 | -   | με    |

| Fall Time                                      | $R_C = 2K\Omega, T_A = 25^{\circ}C$                                               | -   | 0.1            | -   | -      | 0.1 | -   | μs    |

| Total Standby Current: (Note 2) I <sub>S</sub> | V+ = 40V                                                                          | -   | 4              | 10  | -      | 4   | 10  | mA    |

### NOTES:

1. Ramp voltage at Pin 7 Low

where t = OSC period in microseconds

$t \cong R_T C_T$  with  $C_T$  in microfarads and  $R_T$  in ohms.

Output frequency at each output transistor is half OSC frequency when each output is used separately and is equal to the OSC frequency when each output is connected in parallel.

2. Excluding oscillator charging current, error and current limit dividers, and with outputs open.

## Circuit Description

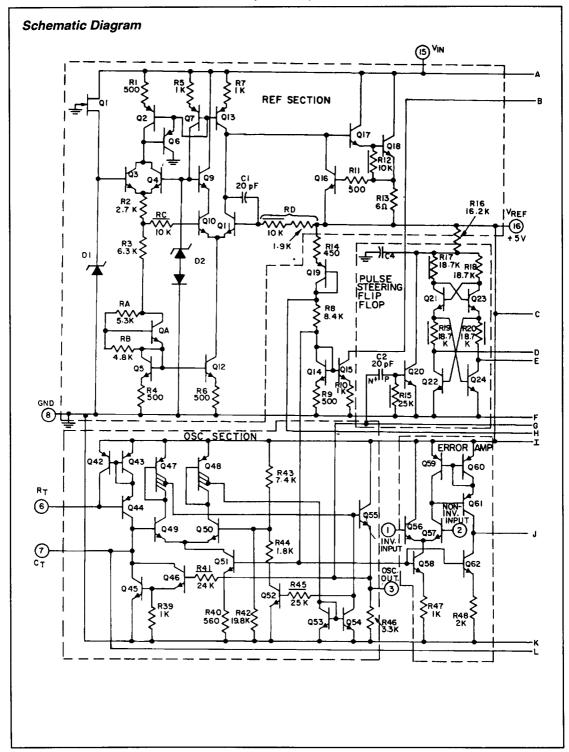

#### Voltage Reference Section

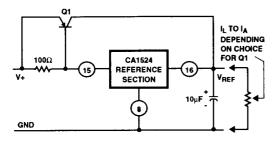

The CAl524 series contains an internal series voltage regulator employing a zener reference to provide a nominal 5-volt output, which is used to bias all internal timing and control circuitry. The output of this regulator is available at terminal l6 and is capable of supplying up to 50mA output current.

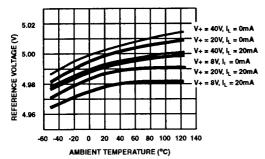

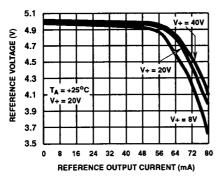

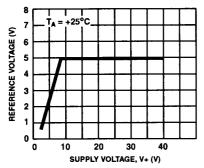

Figure 1 shows the temperature variation of the reference voltage with supply voltages of 8 to 40 volts and load currents up to 20mA. Load regulation and line regulation curves are shown in Figures 2 and 3, respectively.

FIGURE 1. TYPICAL REFERENCE VOLTAGE AS A FUNCTION OF AMBIENT TEMPERATURE

FIGURE 2. TYPICAL REFERENCE VOLTAGE AS A FUNCTION OF REFERENCE OUTPUT CURRENT

FIGURE 3. TYPICAL REFERENCE VOLTAGE AS A FUNCTION OF SUPPLY VOLTAGE

#### **Oscillator Section**

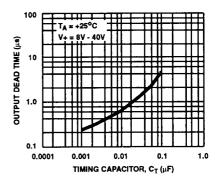

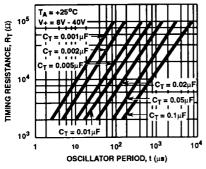

Transistors Q42, Q43 and Q44, in conjunction with an external resistor R<sub>T</sub>, establishes a constant charging current into an external capacitor C<sub>T</sub> to provide a linear ramp voltage at terminal 7. The ramp voltage has a value that ranges from 0.6 to 3.5 volts and is used as the reference for the comparator in the device. The charging current is equal to (5-2V<sub>RF</sub>)/R<sub>T</sub> or approximately 3.6/R<sub>T</sub> and should be kept within the range of 30pA to 2mA by varying R<sub>T</sub>. The discharge time of C<sub>T</sub> determines the pulse width of the oscillator output pulse at terminal 3. This pulse has a practical range of 0.5 µs to 5 µs for a capacitor range of 0.001 to 0.1µF. The pulse has two internal uses: as a dead-time control of blanking pulse to the output stages to assure that both outputs cannot be on simultaneously and as a trigger pulse to the internal flip-flop which controls the switching of the output between the two output channels. The output dead-time relationship is shown in Figure 4. Pulse widths less than 0.5µs may allow false triggering of one output by removing the blanking pulse prior to a stable state in the flip-

FIGURE 4. TYPICAL OUTPUT STAGE DEAD TIME AS A FUNCTION OF TIMING CAPACITOR VALUE

If a small value of  $C_T$  must be used, the pulse width can be further expanded by the addition of a shunt capacitor in the order of 100pF but no greater than 1000pF, from terminal 3 to ground. When the oscillator output pulse is used as a sync input to an oscilloscope, the cable and input capacitances may increase the pulse width slightly. A 2-K $\Omega$  resistor at terminal 3 will usually provide sufficient decoupling of the cable. The upper limit of the pulse width is determined by the maximum duty cycle acceptable.

The oscillator period is determined by  $R_T$  and  $C_T$ , with an approximate value of  $t=R_TC_T$ , where  $R_T$  is in ohms,  $C_T$  is in  $\mu F$ , and t is in  $\mu s$ . Excess lead lengths, which produce stray capacitances, should be avoided in connecting  $R_T$  and  $C_T$  to their respective terminals. Figure 5 provides curves for selecting these values for a wide range of oscillator periods. For series regulator applications, the two outputs can be connected in parallel for an effective 0-90% duty cycle with the output stage frequency the same as the oscillator frequency. Since the outputs are separate, push-pull and flyback applications are possible. The flip-flop divides the frequency such that the duty cycle of each output is 0-45%

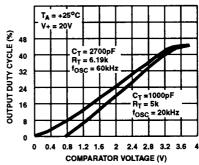

and the overall frequency is half that of the oscillator. Curves of the output duty cycle as a function of the voltage at terminal 9 are shown in Figure 7. To synchronize two or more CAl524's, one must be designated as master, with  $R_T$   $C_T$  set for the correct period. Each of the remaining units (slaves) must have a  $C_T$  of 1/2 the value used in the master and approximately a 1010 longer  $R_TC_T$  period than the master. Connecting terminal 3 together on all units assures that the master output pulse, which occurs first and has a wider pulse width, will reset the slave units.

FIGURE 5. TYPICAL OSCILLATOR PERIOD AS A FUNCTION OF  $R_T$  AND  $C_T$

#### **Error Amplifler Section**

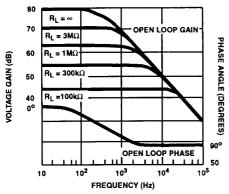

The error amplifier consists of a differential pair (Q56,Q57) with an active load (Q61 and Q62) forming a differential transconductance amplifier. Since Q61 is driven by a constant current source, Q62, the output impedance  $R_{OUT}$  terminal 9, is very high ( $\equiv$  5M $\Omega$ ).

The gain is:

$$A_V = g_m R = 8 \ I_C \ R/2KT = 10^4,$$

where R =  $\frac{R_{OUT} \ R_L}{R_{OUT} + R_L}$  , R<sub>L</sub> =  $\infty$ , A<sub>V</sub>  $\propto 10^4$

Since R<sub>OUT</sub> is extremely high, the gain can be easily reduced from a nominal 10<sup>4</sup> (80dB) by the addition of an external shunt resistor from terminal 9 to ground as shown in Figure 6.

FIGURE 6. OPEN-LOOP ERROR AMPLIFIER RESPONSE CHARACTERISTICS.

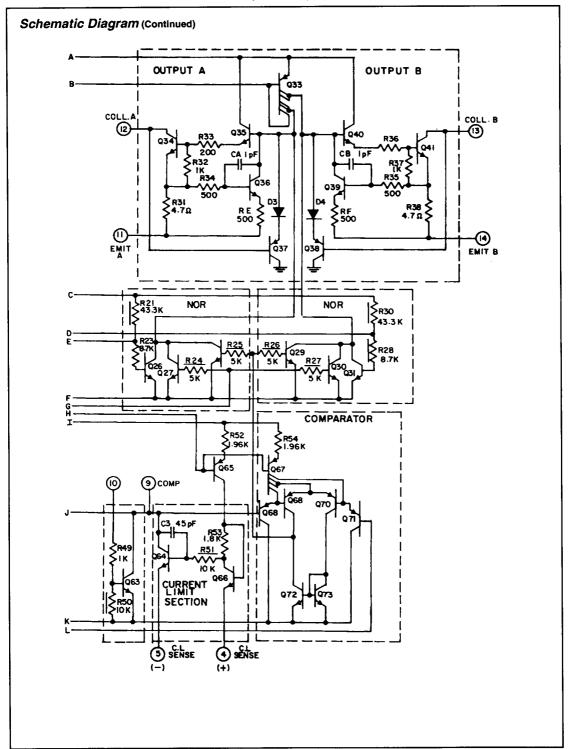

The output amplifier terminal is also used to compensate the system for ac stability. The frequency response and phase shift curves are shown in Figure 7. The uncompensated amplifier has a single pole at approximately 250Hz and a unity gain cross-over at 3MHz.

Since most output filter designs introduce one or more additional poles at a lower frequency, the best network to stabilize the system is a series RC combination at terminal9 to ground. This network should be designed to introduce a zero to cancel out one of the output filter poles. A good starting point to determine the external poles is a 1000-pF capacitor and a variable series 50-K $\Omega$  potentiometer from terminal 9 to ground. The compensation point is also a convenient place to insert any programming signal to override the error amplifier. Internal shutdown and current limiting are also connected at terminal 9. Any external circuit that can sink 200 $\mu$ A can pull this point to ground and shut off both output drivers.

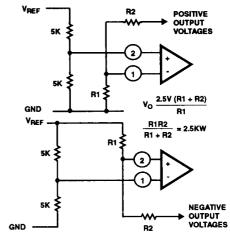

While feedback is normally applied around the entire regulator, the error amplifier can be used with conventional operational amplifier feedback and will be stable in either the inverting or non-inverting mode. Input common-mode limits must be observed; if not, output signal inversion may result. The internal 5-volt reference can be used for conventional regulator applications if divided as shown in Figure 8. If the error amplifier is connected as a unity gain amplifier, a fixed duty cycle application results.

FIGURE 7. TYPICAL DUTY CYCLE AS A FUNCTION OF COMPARATOR VOLTAGE (AT TERMINAL 9).

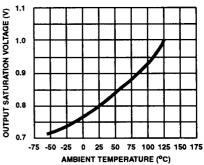

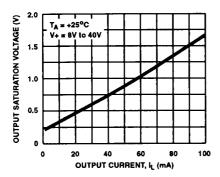

FIGURE 8. TYPICAL OUTPUT SATURATION VOLTAGE AS A FUNCTION OF AMBIENT TEMPERATURE.

#### **Output Section**

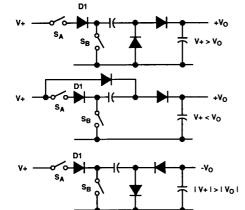

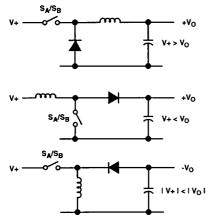

The CA1524 series outputs are two identical n-p-n transistors with both collectors and emitters uncommitted. Each output transistor has antisaturation circuitry that enables a fast transient response for the wide range of oscillator frequencies. Current limiting of the output section is set at 100mA for each output and 100mA total if both outputs are paralleled. Having both emitters and collectors available provides the versatility to drive either n-p-n or p-n-p external transistors. Curves of the output saturation voltage as a function of temperature and output current are shown in Figures 8 and 9, respectively. There area number of output configurations possible in the application of the CA1524 to voltage regulator circuits which fall into three basic classifications:

- 1. Capacitor-diode coupled voltage multipliers

- 2. Inductor-capacitor single-ended circuits

- 3. Transformer-coupled circuits

FIGURE 9. TYPICAL OUTPUT SATURATION VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

#### **Device Application Suggestions**

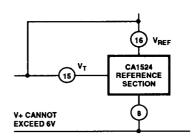

For higher currents, the circuit of Figure 10 may be used with an external p-n-p transistor and bias resistor. The internal regulator may be bypassed for operation from a fixed 5-volt supply by connecting both terminals 15 and 16 to the input voltage, which must not exceed 6 volts.

FIGURE 10. CIRCUIT FOR EXPANDING THE REFERENCE CURRENT CAPABILITY

The internal 5-volt reference can be used for conventional regulator applications if divided as shown in Figure 11. If the error amplifier is connected as a unity gain amplifier, a fixed duty cycle application results.

FIGURE 11. ERROR AMPLIFIER BIASING CIRCUITS

NOTE: V+ Should Be in the 5V Range And Must Not Exceed 6V

## FIGURE 12. CIRCUIT TO ALLOW EXTERNAL BYPASS OF THE REFERENCE REGULATION

To provide an expansion of the dead time without loading the oscillator, the circuit of Figure 13 may be used.

FIGURE 13. CIRCUIT FOR EXPANSION OF DEAD TIME, WITH-OUT USING A CAPACITOR ON PIN 3 OR WHEN A LOW VALUE OSCILLATOR CAPACITOR IS USED

FIGURE 14. FOLDBACK CURRENT-LIMITING CIRCUIT USED TO REDUCE POWER DISSIPATION UNDER SHORTED OUTPUT CONDITIONS

NOTE: Diode D1 Is Necessary To Prevent Reverse Emitter-Base Breakdown of Transistor Switch S<sub>A</sub>

FIGURE 15. CAPACITOR-DIODE COUPLED VOLTAGE MULTIPLIER OUTPUT STAGES

FIGURE 16. SINGLE-ENDED INDUCTOR CIRCUITS WHERE THE TWO OUTPUTS OF THE 1524 ARE CONNECTED IN PARALLEL

TABLE 1. INPUT vs. OUTPUT VOLTAGE, AND FEEDBACK RESISTOR VALUES FOR I<sub>L</sub>=40mA (FOR CAPACITOR-DIODE OUTPUT CIRCUIT IN FIGURE 18)

| V <sub>o</sub> (V) | R <sub>2</sub> (KΩ) | V+ (Min.) (V) |

|--------------------|---------------------|---------------|

| -0.5               | 6                   | 8             |

| -2.5               | 10                  | 9             |

| -3                 | 11                  | 10            |

| -4                 | 13                  | 11            |

| -5                 | 15                  | 12            |

| -6                 | 17                  | 13            |

| -7                 | 19                  | 14            |

| -8                 | 21                  | 15            |

| -9                 | 23                  | 16            |

| -10                | 25                  | 17            |

| -11                | 27                  | 18            |

| -12                | 29                  | 19            |

| -13                | 31                  | 20            |

| -14                | 33                  | 21            |

| -15                | 35                  | 22            |

| -16                | 37                  | 23            |

| -17                | 39                  | 24            |

| -18                | 41                  | 25            |

| -19                | 43                  | 26            |

| -20                | 45                  | 27            |

FIGURE 17. TRANSFORMER-COUPLED OUTPUTS

## Applications\*

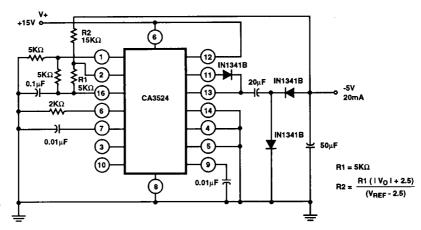

A capacitor-diode output filter is used in Figure 19 to convert +15Vdc to -5Vdc at output currents up to 50mA. Since the output transistors have built-in current limiting, no additional current limiting is needed. Table 1 gives the required minimum input voltage and feedback resistor values, R2, for an output voltage.

#### **Capacitor-Diode Output Circuit**

A capacitor-diode output filter is used in Figure 18 to convert +15Vdc to -5Vdc at output currents up to 50mA. Since the output transistors have built-in current limiting, no additional current limiting is needed. Table 1 gives the required minimum input voltage and feedback resistor values, R2, for an output voltage range of -0.5V to -20V with an output current of 40mA.

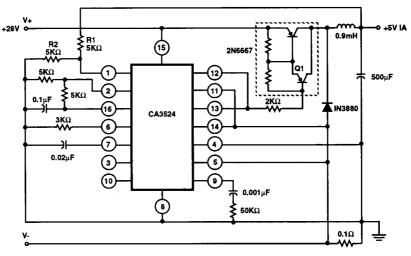

#### Single-Ended Switching Regulator

The CA1524 in the circuit of Figure 19 has both output stages connected in parallel to produce an effective 0% - 90% duty cycle. Transistor Q1 is pulsed on and off by these output stages. Regulation is achieved from the feedback provided by R1 and R2 to the error amplifier which adjusts the on-time of the output transistors according to the load current being drawn. Various output voltages can be obtained by adjusting R1 and R2. The use of an output inductor requires an R-C phase compensation network to stabilize the system. Current limiting is set at 1.9 amperes by the sense resistor R3.

\* For additional information on the application of this device and a further explanation of the circuits below, see RCA Application Note ICAN-691 5 "Application of the CA1524 series PWM IC".

FIGURE 18. CAPACITOR-DIODE OUTPUT CIRCUIT

FIGURE 19. SINGLE-ENDED LC SWITCHING REGULATOR CIRCUIT

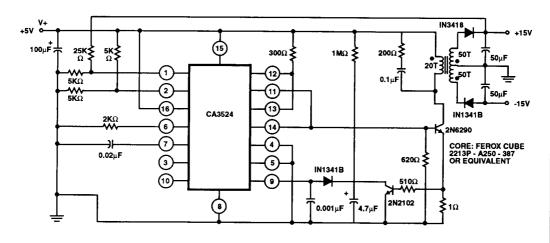

#### **Flyback Converter**

Figure 20 shows a flyback converter circuit for generating a dual 15-volt output at 20mA from a 5-volt regulated line. Reference voltage is provided by the input and the internal reference generator is unused. Current limiting in this circuit is accomplished by sensing current in the primary line and resetting the soft-start circuit.

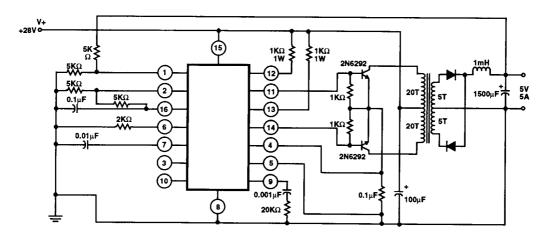

#### **Push-Pull Converter**

The output stages of the CA1524 provide the drive for transistors Q1 and Q2 in the push-pull application of Figure 21. Since the internal flip-flop divides the oscillator frequency by two, the oscillator must be set at twice the output frequency. Current limiting for this circuit is done in the primary of transformer T1 so that the pulse width will be reduced if transformer saturation should occur.

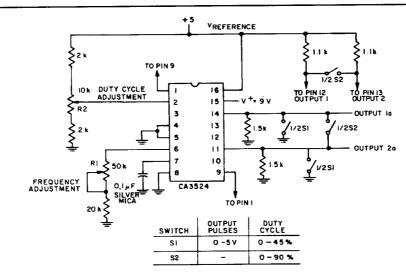

#### **Low-Frequency Pulse Generator**

Figure 22 shows the CA1524 being used as a low-frequency pulse generator. Since all components (error amplifier, oscillator, oscillator reference regulator, output transistor drivers) are on the IC, a regulated 5-V (or 2.5-V) pulse of 0% - 45% (or 0% - 90%) on time is possible over a frequency range of 150 to 500Hz. Switch S1 is used to go from a 5-V output pulse (S1 closed) to a 2.5-V output pulse (S1 open) with a duty cycle range of 0% to 45%. The output frequency will be roughly half of the oscillator frequency when the output transistors are not connected in parallel (75Hz to 250Hz, respectively). Switch S2 will allow both output stages to be paralleled for an effective duty cycle of 0%-90% with the output frequency range from 150 to 500Hz. The frequency is adjusted by R1; R2 controls duty cycle.

FIGURE 20. FLYBACK CONVERTER CIRCUIT

FIGURE 21. PUSH-PULL TRANSFORMER-COUPLED CONVERTER

FIGURE 22. LOW-FREQUENCY PULSE GENERATOR

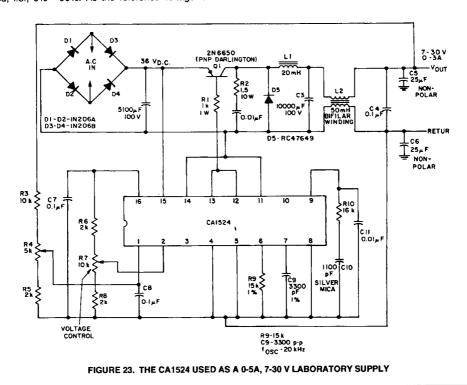

#### The Variable Switcher

The circuit diagram of the CA1524, used as a variable output voltage power supply is shown in Figure 23. By connecting the two output transistors in parallel, the duty cycle is doubled, i.e., 0% - 90%. As the reference voltage level is

varied, the feedback voltage will track that level and cause the output voltage to change according to the change in reference voltage.

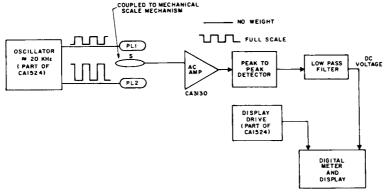

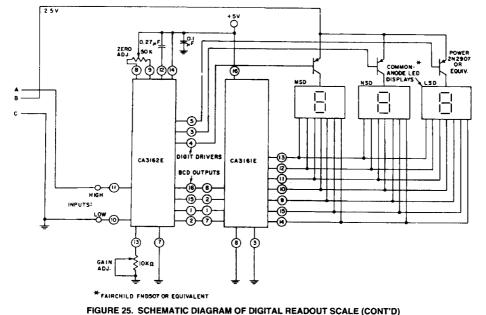

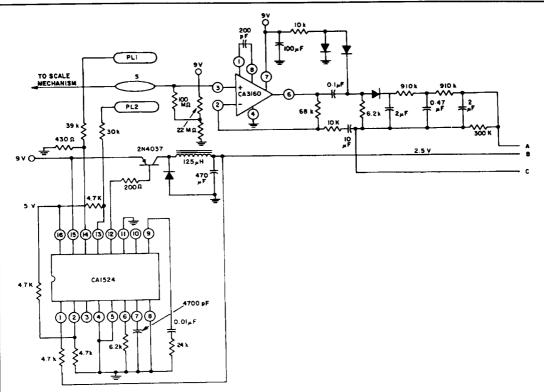

#### **Digital Readout Scale**

The CA1524 can be used as the driving source for an electronic scale application. The circuit shown in Figures 24 and 25 uses half (Q2) of the CA1524 output in a low-voltage switching regulator (2.2V) application to drive the LED's displaying the weight. The remaining output stage (Q1) is used as a driver for the sampling plates PL1 and PL2. Since the CA1524 contains a 5-volt internal regulator and a wide operating range of 8 to 40 volts, a single 9-volt battery can power the total system. The two plates, PL1 and PL2, are driven with opposite phase signals (frequency held constant but duty cycle may change) from the pulse-width modulator IC (CA1524). The sensor, S, is located between the two plates. Plates PL1, S and PL2 form an effective capacitance bridge-type divider network. As plate S is moved according

to the object's weight, a change in capacitance is noted between PL1, S and PL2. This change is reflected as a voltage to the ac amplifier (CA3160). At the null position the signals from PL1 and PL2 as detected by S are equal in amplitude, but opposite in phase. As S is driven by the scale mechanism down toward PL2, the signal at S becomes greater. The CA3160 ac amplifier provides a buffer for the small signal change noted at S. The output of the CA3160 is converted to a dc voltage by a peak-to-peak detector. A peak-to-peak detector is needed, since the duty cycle of the sampled waveform is subject to change. The detector output is filtered further and displayed via the CA3161E and CA3162E digital readout system, indicating the weight on the scale.

FIGURE 24. BASIC DIGITAL READOUT SCALE

DOMESTIC DISCONDING OF DISCONDER OF DISCONDE

FIGURE 26. SCHEMATIC DIAGRAM OF DIGITAL READOUT SCALE

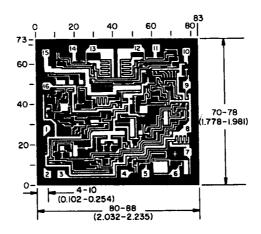

#### **DIMENSIONS AND PAD LAYOUT FOR CA3524RH CHIP**

NOTE: Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils (10<sup>-3</sup> inch). The layout represents a chip when it is part of

the wafer. When the wafer is cut into chips, the cleavage angles are 57° instead of 90° with respect to the face of the chip. Therefore, the isolated chip is actually 7 mils (0.17mm) larger in both dimensions.